### Not Intended For New Designs August 1992

# 11C06 750 MHz D-Type Flip-Flop

# 11C06 750 MHz D-Type Flip-Flop

### **General Description**

The 11C06 is a high-speed ECL D-Type Master-Slave Flip-Flop capable of toggle rates over 750 MHz. Designed primarily for high-speed prescaling, it can also be used in any application which does not require preset inputs. The circuit is voltage-compensated, which makes input thresholds and output levels insensitive to V<sub>EE</sub> variations. Complementary Q and  $\overline{Q}$  outputs are provided, as are two Data inputs, Clock and Clock Enable inputs. The 11C06 is pin-compatible with the Motorola MC1690L but is a higher-frequency replacement.

©1995 National Semiconductor Corporation TL/F/9890

RRD-B30M115/Printed in U. S. A.

# Absolute Maximum Ratings

| Above which the useful life may be impaired                        |  |  |  |  |  |  |

|--------------------------------------------------------------------|--|--|--|--|--|--|

| levices are required,<br>emiconductor Sales<br>and specifications. |  |  |  |  |  |  |

| $-65^{\circ}C$ to $+150^{\circ}C$                                  |  |  |  |  |  |  |

| +150°C                                                             |  |  |  |  |  |  |

| -7.0V to GND                                                       |  |  |  |  |  |  |

| V <sub>EE</sub> to GND                                             |  |  |  |  |  |  |

| -50 mA                                                             |  |  |  |  |  |  |

|                                                                    |  |  |  |  |  |  |

Operating Range-5.7V to -4.7VLead Temperature (Soldering, 10 sec.)300°C

# Recommended Operating Conditions

|                                       | Min   | Тур   | Мах   |

|---------------------------------------|-------|-------|-------|

| Supply Voltage (V <sub>EE</sub> )     | -5.7V | -5.2V | -4.7V |

| Ambient Temperature (T <sub>A</sub> ) | 0°C   |       | +75°C |

# **DC Electrical Characteristics**

| $V_{EE} =$ | $-5.2V, V_{CC} =$ | GND |

|------------|-------------------|-----|

|------------|-------------------|-----|

| Symbol           | Parameter            | Min    | Тур | Max    | Units | TA     | Conditions                                                 |

|------------------|----------------------|--------|-----|--------|-------|--------|------------------------------------------------------------|

| V <sub>OH</sub>  | Output Voltage HIGH  | -1000  |     | -840   | mV    | 0°C    | $V_{IN} = V_{IH (Max)}$ or $V_{IL (Min)}$ per Truth        |

|                  |                      | -960   |     | -810   | mV    | +25°C  | Table Loading 50 $\Omega$ to $-2V$                         |

|                  |                      | -900   |     | -720   | mV    | +75°C  |                                                            |

| V <sub>OL</sub>  | Output Voltage LOW   | - 1870 |     | - 1635 | mV    | 0°C    |                                                            |

|                  |                      | -1850  |     | -1620  | mV    | +25°C  |                                                            |

|                  |                      | - 1830 |     | -1595  | mV    | +75°C  |                                                            |

| V <sub>OHC</sub> | Output Voltage HIGH  | - 1020 |     |        | mV    | 0°C    | $V_{IN} = V_{IH (Min)}$ or $V_{IL (Max)}$ for $D_n$ Inputs |

|                  |                      | -980   |     |        | mV    | +25°C  | Loading 50 $\Omega$ to -2V                                 |

|                  |                      | -920   |     |        | mV    | +75°C  |                                                            |

| V <sub>OLC</sub> | Output Voltage LOW   |        |     | -1615  | mV    | 0°C    |                                                            |

|                  |                      |        |     | -1600  | mV    | +25°C  |                                                            |

|                  |                      |        |     | -1575  | mV    | +75°C  |                                                            |

| VIH              | Input Voltage HIGH   | -1135  |     | -840   | mV    | 0°C    | Guaranteed Input Voltage HIGH                              |

|                  |                      | - 1095 |     | -810   | mV    | +25°C  | for All Inputs                                             |

|                  |                      | - 1035 |     | -720   | mV    | +75°C  |                                                            |

| V <sub>IL</sub>  | Input Voltage LOW    | - 1870 |     | -1500  | mV    | 0°C    | Guaranteed Input Voltage LOW                               |

|                  |                      | - 1850 |     | -1485  | mV    | +25°C  | for All Inputs                                             |

|                  |                      | - 1830 |     | -1460  | mV    | +75°C  | -                                                          |

| IIH              | Input Current HIGH   |        |     |        |       |        | V <sub>IN</sub> = V <sub>IH (Max)</sub>                    |

|                  | Clock Input          |        |     | 250    | μA    | +25°C  |                                                            |

|                  | Data Input           |        |     | 270    | μΑ    | + 25°C |                                                            |

| IIL              | Input Current LOW    | 0.5    |     |        | μΑ    | +25°C  | V <sub>IN</sub> = V <sub>IH (Min)</sub>                    |

| IEE              | Power Supply Current | -59    | -40 |        | mA    | + 25°C | All Inputs Open                                            |

# **AC Electrical Characteristics**

$V_{\mathsf{EE}}=~-5.2\mathsf{V},\,\mathsf{V}_{\mathsf{CC}}=~\mathsf{GND},\,\mathsf{T}_{\mathsf{A}}=~+25^\circ\mathsf{C}$

| Symbol                               | Parameter                                                | Min        | Тур        | Max        | Units    | Conditions          |  |

|--------------------------------------|----------------------------------------------------------|------------|------------|------------|----------|---------------------|--|

| t <sub>PHL</sub><br>t <sub>PLH</sub> | Propagation Delay (CP-Q)<br>Propagation Delay (CP-Q)     | 0.7<br>0.7 | 1.0<br>1.0 | 1.2<br>1.2 | ns<br>ns |                     |  |

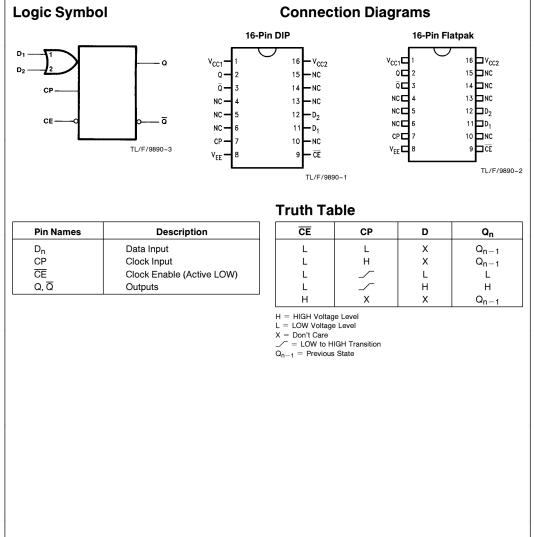

| t <sub>TLH</sub><br>t <sub>THL</sub> | Transition Time 20% to 80%<br>Transition Time 80% to 20% | 0.5<br>0.5 | 0.8<br>0.8 | 1.0<br>1.0 | ns<br>ns | See <i>Figure 1</i> |  |

| ts                                   | Set-up Time                                              |            | 0.2        |            | ns       |                     |  |

| t <sub>H</sub>                       | Hold Time                                                |            | 0.2        |            | ns       | ]                   |  |

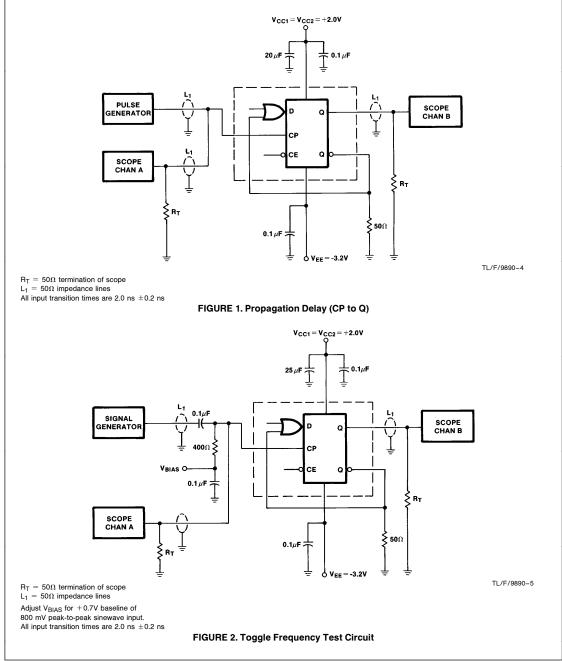

| <sup>f</sup> tog (max)               | Toggle Frequency (CP)                                    | 650        | 750        |            | MHz      | See Figure 2, Note  |  |

Note: The device is guaranteed for f\_{TOG} (CP)  $\geq$  600 MHz, f\_{TOG}(CE)  $\geq$  550 MHz over the 0°C to  $+75^{\circ}C$  temperature range.

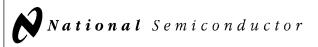

## **Functional Description**

While the clock is LOW, the slave is held steady and the information on the D input is permitted to enter the master. The next transition from LOW to HIGH locks the master in its present state making it insensitive to the D input. This transition simultaneously connects the slave to the master causing the new information to appear on the outputs. Master and slave clock thresholds are internally offset in opposite directions to avoid race conditions or simultaneous

master-slave changes when the clock has slow rise or fall times.

The CP and  $\overline{CE}$  inputs are logically identical, but physical constraints associated with the Dual-In-Line package make the  $\overline{CE}$  input slower at the upper end of the toggle range. To prevent new data from entering the master on the next CP LOW cycle,  $\overline{CE}$  should go HIGH while CP is still HIGH.

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.