# 54/7490A 54LS/74LS90 0/6032 DECADE COUNTER

**DESCRIPTION** — The '90 is a 4-stage ripple counter containing a high speed flip-flop acting as a divide-by-two and three flip-flops connected as a divide-by-five counter. It can be connected to operate with a conventional BCD output pattern or it can be connected to provide a 50% duty cycle output. In the BCD mode, HIGH signals on the Master Set (MS) inputs set the outputs to BCD nine. HIGH signals on the Master Reset (MR) inputs force all outputs LOW. For a similar counter with corner power pins, see the 'LS290; for dual versions, see the 'LS390 and 'LS490.

#### **ORDERING CODE:** See Section 9

|                    | PIN | COMMERCIAL GRADE                                                                         | MILITARY GRADE                                                                                | PKG       |

|--------------------|-----|------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|-----------|

| PKGS               | оит | $V_{CC} = +5.0 \text{ V } \pm 5\%,$<br>$T_A = 0^{\circ}\text{C to } +70^{\circ}\text{C}$ | $V_{CC} = +5.0 \text{ V} \pm 10\%,$<br>$T_A = -55^{\circ}\text{ C to} + 125^{\circ}\text{ C}$ | 10%, TVDE |

| Plastic<br>DIP (P) | A   | 7490APC, 74LS90PC                                                                        |                                                                                               | 9A        |

| Ceramic<br>DIP (D) | А   | 7490ADC, 74LS90DC                                                                        | 5490ADM, 54LS90DM                                                                             | 6A        |

| Flatpak<br>(F)     | Α   | 7490AFC, 74LS90FC                                                                        | 5490AFM, 54LS90FM                                                                             | 31        |

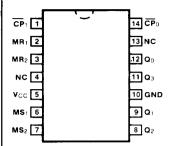

# CONNECTION DIAGRAM PINOUT A

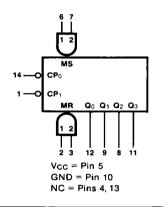

### LOGIC SYMBOL

### INPUT LOADING/FAN-OUT: See Section 3 for U.L. defintions

| PIN NAMES                         | DESCRIPTION                                                | <b>54/74 (U.L.)</b><br>HIGH/LOW | 54/74LS (U.L.)<br>HIGH/LOW |

|-----------------------------------|------------------------------------------------------------|---------------------------------|----------------------------|

| CP₀                               | ÷2 Section Clock Input<br>(Active Falling Edge)            | 2.0/2.0                         | 0.125/1.5                  |

| CP₁                               | ÷5 Section Clock Input (Active Falling Edge)               | 3.0/3.0                         | 0.250/2.0                  |

| MR <sub>1</sub> , MR <sub>2</sub> | Asynchronous Master Reset Inputs (Active HIGH)             | 1.0/1.0                         | 0.5/0.25                   |

| MS <sub>1</sub> , MS <sub>2</sub> | Asynchronous Master Set<br>(Preset 9) inputs (Active HIGH) | 1.0/1.0                         | 0.5/0.25                   |

| Q <sub>0</sub>                    | ÷2 Section Output*                                         | 20/10                           | 10/5.0<br>(2.5)            |

| Q1 — Q3                           | ÷5 Section Outputs                                         | 20/10                           | 10/5.0<br>(2.5)            |

<sup>\*</sup>The  $Q_0$  output is guaranteed to drive the full rated fan-out plus the  $\overline{\mbox{CP}}_1$  input.

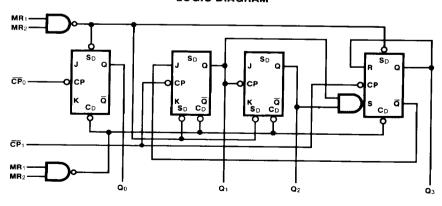

FUNCTIONAL DESCRIPTION — The '90 is a 4-bit ripple type decade counter. It consists of four master/slave flip-flops which are internally connected to provide a divide-by-two section and a divide-by-five section. Each section has a separate clock input which initiates state changes of the counter on the HIGH-to-LOW clock transition. State changes of the Q outputs do not occur simultaneously because of internal ripple delays. Therefore, decoded output signals are subject to decoding spikes and should not be used for clocks or strobes. The Q<sub>0</sub> output of each device is designed and specified to drive the rated fan-out plus the  $\overline{\mathbb{CP}}_1$  input. A gated AND asynchronous Master Reset (MR<sub>1</sub>, MR<sub>2</sub>) is provided which overrides the clocks and resets (clears) all the flip-flops. A gated AND asynchronous Master Set (MS<sub>1</sub>, MS<sub>2</sub>) is provided which overrides the clocks and the MR inputs and sets the outputs to nine (HLLH). Since the output from the divide-by-two section is not internally connected to the succeeding stages, the devices may be operated in various counting modes.:

- A. BCD Decade (8421) Counter—The  $\overline{CP}_1$  input must be externally connected to the Q<sub>0</sub> output. The  $\overline{CP}_0$  input receives the incoming count and a BCD count sequence is produced.

- B. Symmetrical Bi-quinary Divide-By-Ten Counter The  $Q_3$  output must be externally connected to the  $\overline{CP}_0$  input. The input count is then applied to the  $\overline{CP}_1$  input and a divide-by-ten square wave is obtained at output  $Q_0$ .

- C. Divide-By-Two and Divide-By-Five Counter No external interconnections are required. The first flip-flop is used as a binary element for the divide-by-two function ( $\overline{CP}_0$  as the input and  $Q_0$  as the output). The  $\overline{CP}_1$  input is used to obtain binary divide-by-five operation at the  $Q_3$  output.

#### MODE SELECTION

| RESET/SET INPUTS |                 |                 | OUTPUTS         |       |                |                |                |

|------------------|-----------------|-----------------|-----------------|-------|----------------|----------------|----------------|

| MR <sub>1</sub>  | MR <sub>2</sub> | MS <sub>1</sub> | MS <sub>2</sub> | $Q_0$ | Q <sub>1</sub> | Q <sub>3</sub> | Q <sub>3</sub> |

| Н                | Н               | L               | Х               | L     | L              | L              | L              |

| H                | н               | Х               | L               | L     | L              | L              | L              |

| X                | Х               | Н               | Н               | н     | L              | L              | н              |

| L                | Х               | L               | Х               | l     | Co             | unt            |                |

| X                | L               | Х               | L               |       | Co             | unt            |                |

| L                | Х               | Х               | L               |       | Co             | unt            |                |

| Х                | L               | L               | Х               |       | Co             | unt            |                |

|                  |                 |                 |                 |       |                |                |                |

H = HIGH Voltage Level

L = LOW Voltage Level

X = Immaterial

#### **BCD COUNT SEQUENCE**

| COUNT | OUTPUTS |                |                |                |  |  |  |

|-------|---------|----------------|----------------|----------------|--|--|--|

|       | Q       | Q <sub>1</sub> | Q <sub>2</sub> | Q <sub>3</sub> |  |  |  |

| 0     | L       | L              | L              | L              |  |  |  |

| 1     | н       | L              | L              | L              |  |  |  |

| 2     | L       | H              | L              | L              |  |  |  |

| 3     | Н       | Н              | L              | L              |  |  |  |

| 4     | L       | L              | Н              | L              |  |  |  |

| 5     | н       | L              | Н              | L              |  |  |  |

| 6     | L       | Н              | Н              | L              |  |  |  |

| 7     | Н       | Н              | Н              | L              |  |  |  |

| 8     | L       | L              | L              | Н              |  |  |  |

| 9     | Н       | L              | L              | Н              |  |  |  |

NOTE: Output Q<sub>0</sub> is connected to Input  $\overline{CP}_1$  for BCD count.

#### LOGIC DIAGRAM

| SYMBOL | PARAMETER               | 54/74   | 54/74LS | UNITS  | CONDITIONS                                     |

|--------|-------------------------|---------|---------|--------|------------------------------------------------|

|        |                         | Min Max |         | Olding | CONDITIONS                                     |

| Ін     | Input HIGH Current, CPo | 1.0     | 0.2     | mA     | V <sub>CC</sub> = Max, V <sub>IN</sub> = 5.5 V |

| ин     | Input HIGH Current CP1  | 1.0     | 0.4     | mA     | V <sub>CC</sub> = Max, V <sub>IN</sub> = 5.5 V |

| lcc    | Power Supply Current    | 42      | 15      | mA     | V <sub>CC</sub> = Max                          |

## AC CHARACTERISTICS: $V_{CC} = +5.0 \text{ V}$ , $T_A = +25^{\circ} \text{ C}$ (See Section 3 for waveforms and load configurations)

|                  | PARAMETER                                                    |     | 54/74                               |     | 74LS     |       |                 |  |

|------------------|--------------------------------------------------------------|-----|-------------------------------------|-----|----------|-------|-----------------|--|

| SYMBOL           |                                                              |     | $C_L = 15 pF$<br>$R_L = 400 \Omega$ |     | 15 pF    | UNITS | CONDITIONS      |  |

| [<br>            |                                                              | Min | Max                                 | Min | Max      |       |                 |  |

| f <sub>max</sub> | Maximum Count Frequency, CPo                                 | 32  |                                     | 32  |          | MHz   | Figs. 3-1, 3-9  |  |

| f <sub>max</sub> | Maximum Count Frequency, CP1                                 | 16  |                                     | 16  |          | MHz   | Figs. 3-1, 3-9  |  |

| tpLH<br>tpHL     | Propagation Delay CPo to Qo                                  |     | 16<br>18                            |     | 16<br>18 | ns    | Figs. 3-1, 3-9  |  |

| tpLH<br>tpHL     | Propagation Delay<br>CP <sub>0</sub> to Q <sub>3</sub>       |     | 48<br>50                            |     | 48<br>50 | ns    | Figs. 3-1, 3-9  |  |

| tpLH<br>tpHL     | Propagation Delay<br>CP1 to Q1                               |     | 16<br>21                            |     | 16<br>21 | ns    | Figs. 3-1, 3-9  |  |

| tpLH<br>tpHL     | Propagation Delay<br>CP <sub>1</sub> to Q <sub>2</sub>       |     | 32<br>35                            |     | 32<br>35 | ns    | Figs. 3-1, 3-9  |  |

| tpuh<br>tphu     | Propagation Delay<br>CP <sub>1</sub> to Q <sub>3</sub>       |     | 32<br>35                            |     | 32<br>35 | ns    | Figs. 3-1, 3-9  |  |

| tpLH             | Propagation Delay<br>MS to Q <sub>0</sub> and Q <sub>3</sub> |     | 30                                  |     | 30       | ns    | Figs. 3-1, 3-17 |  |

| tpHL             | Propagation Delay<br>MS to Q <sub>1</sub> and Q <sub>3</sub> |     | 40                                  |     | 40       | ns    | Figs. 3-1, 3-17 |  |

| tpHL             | Propagation Delay<br>MR to Q <sub>n</sub>                    |     | 40                                  |     | 40       | ns    | Figs. 3-1, 3-17 |  |

## AC OPERATING REQUIREMENTS: $V_{CC} = +5.0 \text{ V}, T_A = +25^{\circ} \text{ C}$

| SYMBOL             | PARAMETER               | 54/74   | 54/74LS | UNITS | CONDITIONS |

|--------------------|-------------------------|---------|---------|-------|------------|

|                    |                         | Min Max | Min Max |       |            |

| t <sub>w</sub> (H) | CP₀ Pulse Width HIGH    | 15      | 15      | ns    | Fig. 3-9   |

| tw (H)             | CP1 Pulse Width HIGH    | 30      | 30      | ns    | Fig. 3-9   |

| tw (H)             | MS Pulse Width HIGH     | 15      | 15      | ns    | Fig. 3-17  |

| t <sub>w</sub> (H) | MR Pulse Width HIGH     | 15      | 15      | ns    | Fig. 3-17  |

| trec               | Recovery Time, MS to CP | 25      | 25      | ns    | Fig. 3-17  |

| trec               | Recovery Time, MR to CP | 25      | 25      | ns    | Fig. 3-17  |