408-906

# MM57C200 ENCODER / DECODER

## General Description

The MM57C200 is an ENCODER/DECODER circuit with MM53200 compatible functions. It requires few external components to operate as transmitter or as a receiver. Three different modes are provided with a maximum of 1M codes. The ENCODER/DECODER IC is designed in M2CMOS technology.

## Typical Applications

- \* Burglar alarm systems

- Remote control

- Central locking systems

- Valve control

## Features

- Simple RC oscillator with 1% tolerance for R and 5% for C

- \* Up to 1M encoding possibilities

- \* Three different modes

- Transmitter burst-mode for infrared transmission

- Few external components

- SO-20 Wide package available

- M2CMOS-technology

- \* Programmable output polarity

- \* Time delay after false code

- Up to 8 outputs can be driven

- \* Latched and normal output mode

- \* Receiver learn mode \*

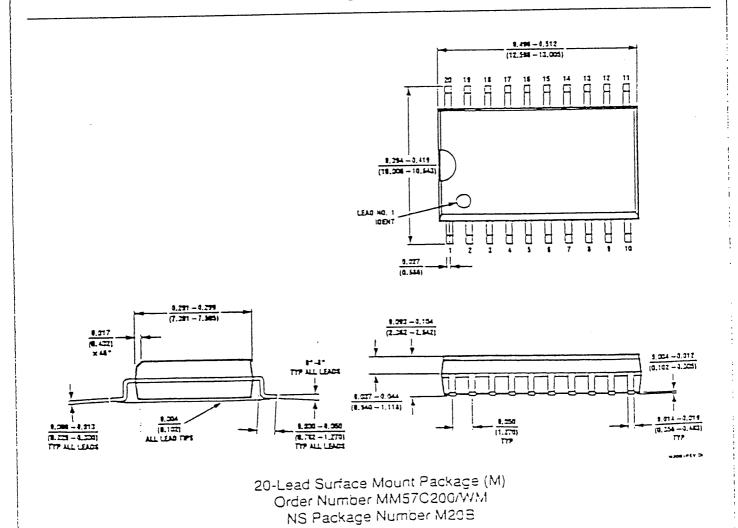

Figure 1: 20-Pin DIP - Top View

## GENERAL

The device has three different operating modes: Mode I, a simple MM53200 compatible mode, Mode II, a enhanced MM53200 compatible mode in which the receiver code can be programmed via the transmitter and Mode III, a high feature mode with a 20 bit code and 8 additional outputs. After a task is executed the chip starts scanning the mode again. This precaution eliminates erroneously detected code from faulty or destroyed RAM data (encoded data from the code-select lines, or the mode word) which will be updated (recovered) if malfunctions occur.

## MODE SELECT

For modes XMIT I, XMIT II and Receive I, mode select achieved by connecting pins MF1, MF2 and MF3 a shown in table 1. For modes Receive II, Receive III ar XMIT III, mode select information has to be programme into the EEPROM as shown in table 2.

To find out which mode is selected, the chip checks if EEPROM is connected and reads in the EEPROM information, or scans the mode pins MF1 to MF3 if no EIPROM is connected.

### MODEI

In this mode code is selected via the code-select lines SL1 to SL12 giving a total of 4096 codes.

When selected as transmitter the chip reads the status of code-select lines SL1 to SL12, checks if burst transmission has been selected and if the receiver output toggles. It transmits this information serially over the TxD pin.

When selected as receiver, the chip looks for a valid transmission (see section RECEIVE). In case of a valid received code, output MF1 is activated as long as the reception is acceptable. If the transmitter was in latched mode, the receiver output toggles and remains unchanged until a new received code is valid.

### MODE II

In this mode, code is selected at the transmitter via the code-select lines SL1 to SL12 and the receiver code is stored in the EEPROM, so there is also a total of 4096 codes. The EEPROM can contain two codes, a basic code which is used for first communication and a extended code which can be programmed via the transmitter. To control the receiver put the code-select lines at the transmitter into the same status as the basic code in the receiver EEPROM. Now you can either control the receiver output MF1 in the same way as in mode I or put the receiver into learn mode.

When selected as transmitter the chip acts in the same way as in mode I and additionally scans pin MF3 for learn information.

When selected as receiver, the chip looks if MF3 is pulled low for longer than 2 seconds which indicates that the basic code shall be used as valid code from now on. By reactivating the basic code the chip activates output MF2 for 2 seconds to indicate that the basic code is now reprogrammed. If the basic code was valid MF2 is not activated. Further, the chip scans for a valid transmission (see section RECEIVE). In case of a valid reception output MFt is either tied low as long as the reception is acceptable or toggles if the transmitter requests the receiver output to toggle. The third possibility is that the transmitted information puts the receiver into the learn mode. Note that the Receiver goes only into learn mode if the transmitted code is valid and the learn bit in the transmitted code is set. Now the receiver activates output MF2 and enters learn mode. In the following 45 seconds (approximately) the receiver accepts each code which is received twice as new code which we will call the extended code. The receiver exits the learn mode and inactivates MF2 either if an extended code is received or the time limit is exceeded. Note that the basic code is not destroyed and you can switch back to the basic code at any time by pulling the receiver's MF2 pin law for longer than 2 seconds. This is useful if something went wrong when programming the extended code.

### MODE III

This is the ultra high coding mode. Mode select information and a 20 bit code are stored in the transmitter and the receiver EEPROM. So there are over 1 million codes. Additional information from the transmitter code-select lines SL1 to SL8 is appended and transmitted with the code. This additional information will be copied to the receiver pins SL1 to SL8 which are used as outputs in this mode.

When selected as transmitter the chip transmits the 20 bit key from the EEPROM and the status of the code-select lines SL1 to SL8. This block is transmitted with latched bit set or reset depending on the level of pin MF2, either in normal or in burst mode.

When selected as receiver the chip looks for a valid transmission (see section RECEIVE). In case of a valid reception output MF1 is either tied low as long as the reception is acceptable or toggles if the transmitter determines the receiver output to toggle. Additionally the pins SL1 to SL8 are switched as outputs corresponding to the information transmitted. Another feature is that you can determine if the 8 additional dedicated outputs are active-low or active-high and also if they are latched or unlatched. For further information please refer to table 3.

### RECEIVE

If the received code matches with the right format the ENCODER/DECODER looks for a second transmission which must be equal to the first transmission to prevent a receive error. If both transmissions are equal the receiver returns if in the learn mode. If it was not in learn mode the chip reads in its own code either from the code-select lines or from the EEPROM depending on the selected mode and compares it with the received code. If both codes are identical the transmission is valid otherwise the transmission is invalid. If the transmission is invalid a timedelay of 2 seconds is initiated and the chip continues with scanning the mode again. This precaution is implemented in order to avoid 'misuse'. This means, it is not possible to find out and send the right 'code combination', (by successively trying different codes), in a realistic period of time. Note that there is a difference between a receive error and an invalid transmission which causes the receiver to do a time delay. A receive error happens if no code is received. the received code has not the right formation two received codes are not identical. However, an invalid transmission will occur if the transmitted code is not identical to the receiver code but in the right format.

## TRANSMIT

When the circuit is selected as a transmitter, it creates a PWM pulse sequence of the code it has identified after scanning the code-select lines or reading the EEPROM and scanning the mode pins. See timing diagram.

## USING A EEPROM

When using a EEPROM please refer to table 2, 3 and 4.

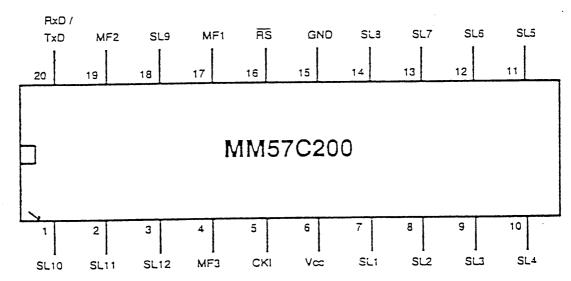

## PIN DESCRIPTION

#### SL1-SL8 Code select lines 1 to 8

These pins are dedicated for encoding purposes in mode XMIT I  $\star$  II and Receive I. They are dedicated as information inputs in mode XMIT III, and as outputs for this information in mode Receive III. They are unused in mode Receive II. These pins are provided with internal pull-ups and input switches should pull them to ground.

#### SL9-SL12 Code-select lines 9 to 12

These pins are dedicated for encoding purposes in mode XMIT I + II and Receive I. They are used as serial interface to a external EEPROM in mode XMIT III and Receive II + III. Note that only SL9 to SL11 have internal pull-ups but not SL12.

#### MF1 Multi-function pin 1

This pin serves as output in all receiver modes and as input which determines if the key is to be transmitted in normal or burst format for all transmitter modes. It has an on-chip pull-up.

#### MF2 Multi-function pin 2

In all transmit modes these pin determines if the receiver output is latched or normal. In mode Receive I, MF2 is used as mode-select pin which must be left open circuited. In mode Receive II, MF2 serves as LEARN-INDICATE output. It has an on-chip pull-up and is not used in mode Receive III.

### MF3 Multi-function pin 3

In mode XMIT I and Receive I this pin is a mode-select pin. In mode XMIT II it determines if the receiver shall initiate a learn cycle. In mode Receive II it is an input which has to be grounded for longer than 2 seconds to retrieve the basic-code. It is not used in mode XMIT III and Receive III. Note that this pin is not provided with an internal pull-up.

#### RxD/TxD Receive/transmit pin

Configured as receiver this pin receives the pulse-width modulated signals from the detector. Selected as transmitter this pin transmits the pulse-width modulated signals either in normal or in burst-format.

#### CKI RC oscillator input

Allowed tolerances: Delta R/R = +/-1 %Delta C/C = +/-5 %

#### RS System reset input

An RC network is required with a diode in parallel to R. RC time constant 5 times power supply rise time.

GND System ground

Vcc System power supply

## Table 1: Mode select depending on MF1, MF2 and MF3

| MF1    | MF2  | MF3                      | MODE *see Nate 1     |                    |  |

|--------|------|--------------------------|----------------------|--------------------|--|

| OUTPUT | open | open GND                 |                      |                    |  |

| ореп   | GND  | Vcc                      | XMIT I/II<br>latched | NORMAL             |  |

| open   | apen | Vcc XMIT I/II<br>MM53200 |                      | TRANSFER           |  |

| GND    | GND  | Vcc                      | XMIT I/II<br>latched | BURST<br>TRANSFER  |  |

| GND    | open | Vcc                      | XMIT I/II<br>MM53200 |                    |  |

| open   | GND  | GND                      | XMIT II<br>learn     | NORMAL<br>TRANSFER |  |

| GND    | GND  | GND                      | XMIT II<br>leam      | BURST<br>TRANSFER  |  |

Table 2: Mode-select information in the EEPROM

| bit 9 | bit 8 | mode        |

|-------|-------|-------------|

| 0     | 1     | Receive II  |

| 1     | 0     | XMIT III    |

| 0     | 0     | Receive III |

Additional mode select information is stored in the EEPROM in register 0D bit 8 and 9. Burst/normal-Transfer and MM53200 compatible or latched output are controlled with Transmitter-pins MF1 and MF2 in the same way as shown in table 1. This mode information is only accepted if the EE-PROM-ID is correct. This ID is to be located in register 0D bit 0 to 7 and MUST be set to 047 (hex).

Table 3: Additional output configuration in EEPROM Reg. "D"

| CASE | BIT B | BIT A | Comments                                                                                                                                                                                                                                                                                                                                                   |

|------|-------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | 0     | 0     | Receiver outputs SL1 - SL8 are logical "0" after power on and after Reset.  If valid data is sent from a transmitter, the open transmitter will cause the corresponding output of the receiver to be switched high. When transmission stops the outputs will return to "0" level.                                                                          |

| 2    | 0     | 1     | Receiver output states are the invers of case 1.  Receiver outputs SL1 - SL8 are logical "1" after power on and after Reset.  If valid data is sent from a transmission, the open switches at SL1 - SL8 of the transmitter will cause the corresponding output of the receiver to be turned off.  When transmission stops, the output return to "1" level. |

| 3    | 1     | 0     | Same as Case 1, but outputs of receiver remain latched until new combination of SL1 - SL8 data will be sent by transmitter.                                                                                                                                                                                                                                |

| 4    | 1     | 1     | Same as case 2, but outputs of receiver remain latched until new combination on SL1 - SL8 data will be sent by transmitter.                                                                                                                                                                                                                                |

Table 4: Code-data in EEPROM in mode Receive II and XMIT/Receive III

| mode | register | bit   |                                                                   |

|------|----------|-------|-------------------------------------------------------------------|

| II . | 00       | 00-08 | learn-key 1 to 12                                                 |

|      | 00       | 00    | basic-code bit  If this bit is set to '1' the basic-code is used. |

|      | OF       | 00-0B | basic-code bit 1 to 12                                            |

| Ш    | 0E       | 00-0F | key bit 1 to 16                                                   |

|      | 0F       | 00-03 | key bit 17 to 20                                                  |

# Transmit timings Mode I and II (compatible to MM53200) 11.52 ms **Block** $t_P = 11.52 \, \text{ms}$ start bit 0.32 ms for all modes 0.96 ms Mode I and II in latched or learn mode 12.48 ms pause time 1 start bit additional Bit for latched or learn information Mode III 27.84 ms pause 8 output bits (for St. 1 - St.8) time 20 code bits "latched" bit determines - 1 start bit if output MF1 is latched or in MM53200 mode. burst Transmission logical output: output signal:

output signal:

Please note: all timings given here are typical and vary with the clock tolerances

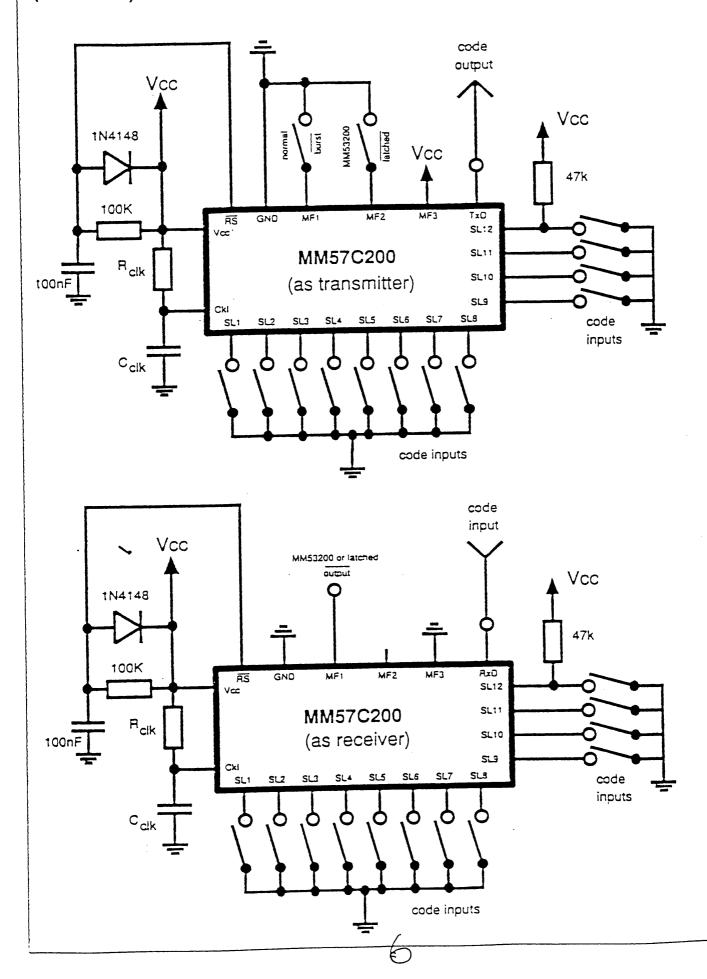

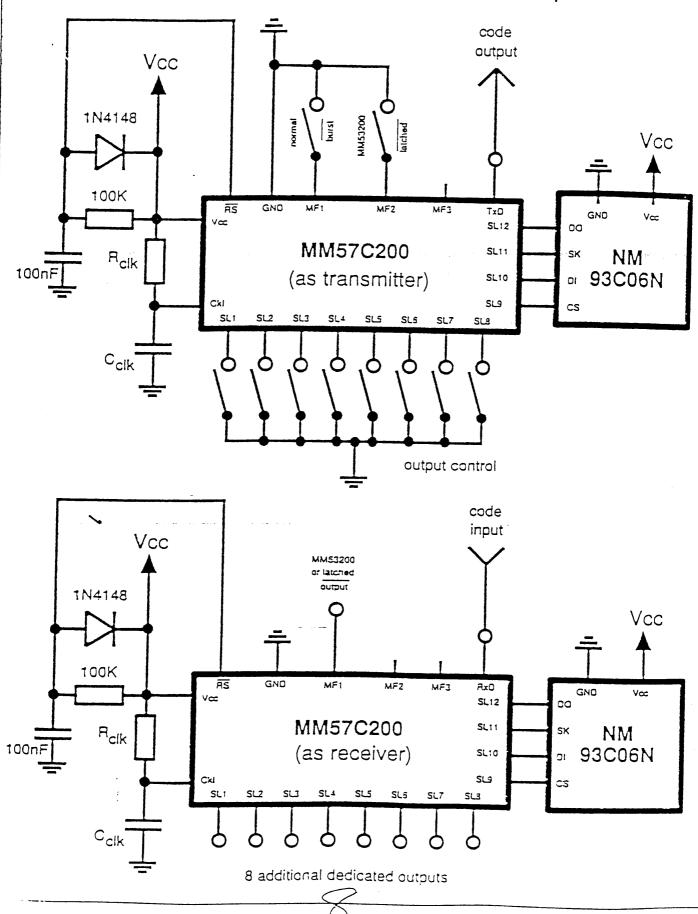

Figure 2: MM57C200 in MM53200 compatible (Mode I) transmit / receive mode.

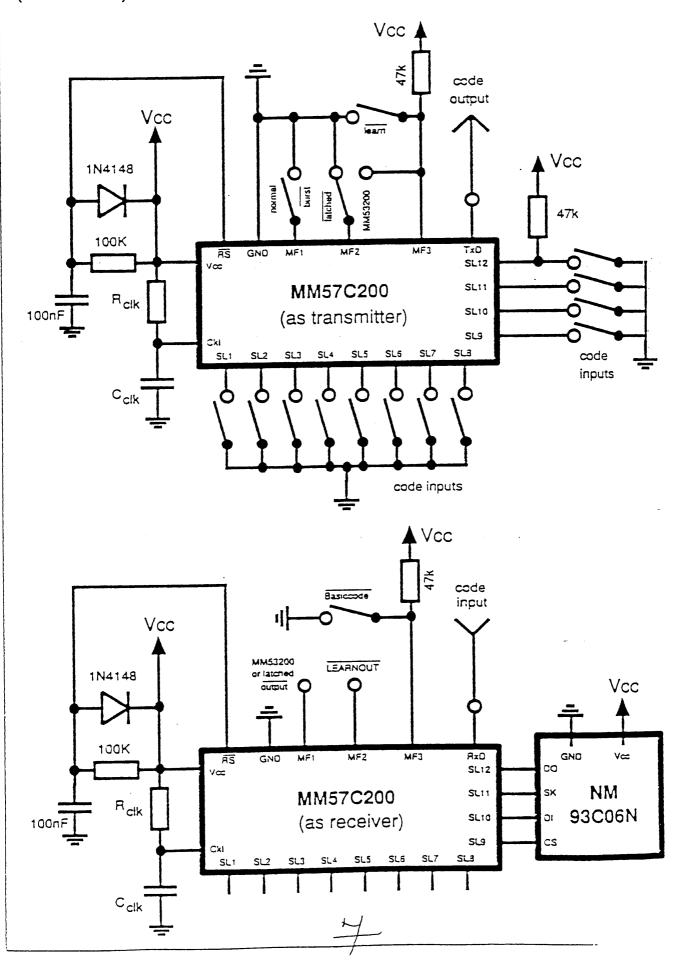

Figure 3: MM57C200 in MM53200 compatible trans-(Mode II) mit mode, receiver code in EEPROM

Figure 4: Ultra high coding mode (transmitter (Mode III) and receiver code in EEPROM) + 8 additional dedicated outputs.

# MM57C200 Absolute Maximum Ratings

If Military / Aerospace specified devices are required, please contact the National Semiconductor Sales Office / Distributors for availability and specifications.

Total Current out of GND Pin (Sink) Storage Temperature Range 60 mA -65°C to +140°C

Supply Vortage (Vcc) Vortage at any Pin ESO Susceptibility (Note 3) Total Current into Vcc Pin (Source)

7V -0.3V to Vcc + 0.3V 2000V 50 mA Note: Absolute maximum ratings indicate limits beyond which damage to the device may occur. DC and AC electrical specifications are not ensured, when operating the device at absolute maximum ratings.

| Parameter                               | Condition                   | Min     | Тур      | Max     | Unit |

|-----------------------------------------|-----------------------------|---------|----------|---------|------|

| Operating Voltage                       | Rclk = 3.3kOhm              | 4.5     |          | 6.0     | ٧    |

| g                                       | Cclk = 100pF                |         |          |         |      |

|                                         | Rclk = 6.8kOhm              | 2.5     |          | 6.0     | ٧    |

|                                         | Cclk = 100pF                |         |          |         |      |

| Power Supply Ripple (Note 1)            | Peak to Peak                |         |          | 0.1 Vcc | V    |

| Supply Current (Note4)                  |                             |         |          |         |      |

| Rak = 3.3kOhm, Cak = 100pF              |                             |         |          |         |      |

| Tc ~ 5.33 usec                          | 5 V                         |         | 2.52     | .       | mΑ   |

| Rak = 6.8kChm, Cak = 100pF              | 3 V                         |         | 0.66     |         | mΑ   |

| Tc - 11 usec                            | 5 V                         | _       | 1.74     |         | mΑ   |

| Input Levels                            |                             |         |          |         |      |

| RS, CKI                                 | **                          |         |          |         |      |

| Logic High                              |                             | 0.9 Vcc |          |         | ٧    |

| Logic Low                               |                             |         |          | 0.1 Vcc | ٧    |

| All Other Inputs                        |                             |         |          |         |      |

| Logic High                              |                             | 0.7 Vcc |          |         | ٧    |

| Logic Low                               |                             |         |          | 0.2 Vcc | V    |

| Hi-Z Input Leakage                      | Vcc=6.0V, Vin=0V            | -2      |          | +2      | uА   |

| Input Pullup Current                    | V∞=6.0V, Vin=0V             | 40      |          | 250     | uΑ   |

| Input Hysteresis                        |                             |         |          |         |      |

| MF1.2.3. SL9-12.RxD                     |                             |         | 0.05 Vcc |         | V    |

| Output Current Levels                   |                             |         |          |         |      |

| Source (Weak Pull-Up)                   | Vcc=4.5V, Voh=3.2V          | 10      |          | 110     | uА   |

|                                         | Vcc=2.5V, Voh=1.8V          | 2.5     |          | 33      | uА   |

| Source (Push-Pull Mode)                 | Vcc=4.5V, Voh=3.8V          | 0.4     |          |         | mA   |

| •                                       | $V\infty=2.5V$ , $Voh=1.8V$ | 0.2     |          |         | mΑ   |

| Sink (Push-Pull Mode)                   | Vcc=4.5V, Val=0.4V          | 1.6     |          |         | mΑ   |

|                                         | Vcc=2.5V, Vol=0.4V          | 0.7     |          |         | mΑ   |

| TRI-STATE Leakage                       |                             | -2.0    |          | +2.0    | uА   |

| Allowable Sink/Source                   |                             |         |          |         |      |

| Current Per Pin                         |                             |         |          | 3       | mA   |

| Maximum Input Current                   |                             |         |          |         |      |

| Without Latchup (Note 2)                | Room Temp                   |         |          | +/- 100 | mA   |

| RAM Retention Voltage, Vr               | 500 ns Rise and             |         |          |         |      |

| , , , , , , , , , , , , , , , , , , , , | Fall Time (Min)             | 2.0     |          |         | V    |

|                                         |                             | 1       |          | 7       |      |

Input Capacitance

Note 1: Rate of voltage change must be less than 0.5V/ms

Note 2: Except pins SL12, MF3, AS

pins SL12, AS +60mA, -100mA pin MF3 +100mA,-25mA

Sampled but not 100% tested.

Note 3: Human body model, 100pF through 1500 Ohm. Note 4: AS ited to nich, all other in- and outbuts open.

9

# MM57C200

| AC Electrical Character                  | istics -40°C<=       | T _<=+85 | °C unless | otherwise | specified |

|------------------------------------------|----------------------|----------|-----------|-----------|-----------|

| Parameter                                | Condition            | Min      | Тур       | Max       | Units     |

| Inputs                                   |                      |          |           |           |           |

| tsetup                                   | Vcc>=4.5V            | 200      |           |           | ns        |

|                                          | 2.5V<=Vcc<4.5V       | 500      |           |           | ns        |

| t HGL2                                   | Vcc>=4.5V            | 60       |           |           | ns        |

| 760                                      | 2.5V<=Vcc<4.5V       | 150      |           |           | ns        |

| Output Propagation Delay                 | C_=100pF R_= 2.2kChm |          |           |           |           |

| t <sub>POT</sub> , t <sub>POO</sub>      | Vcc>=4.5V            |          |           | 0.7       | us        |

| SL10, SL11                               | 2.5V<=Vcc<4.5V       |          |           | 1.75      | us        |

| <b>*</b> # <b>G</b> V                    | Vcc>=4.5V            |          |           | 1         | us        |

| All Others                               | 2.5V<=Vcc<4.5V       |          |           | 2.5       | us        |

| MICROWIRE Setup Time tuws                |                      | 20       |           |           | пѕ        |

| MICROWIRE Hold Time by                   |                      | 56       |           |           | ns        |

| MICROWIRE Output                         |                      |          |           | 220       | пѕ        |

| Propagation Delay tupo Reset Pulse Width |                      | 1.0      |           |           | us        |

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

Rabbeal Semicroscotter Seman Industriestrade ID G-8080 Furstrentendruck Tel (9.31-41) 103-3 Feex (9.31-41) 10.25-54

Metoonal Semicodoctor (UK) List. The Madie, Cemorey Park Swindon Winshire SNZ SUT Tel: (07 33) 51 44 41 Telez AAA 574 Fiz: (07 33) 59 75 22 Rational

Lomporatorior S.A.

Centre 1 Affairs 14.3 BourtidiereBâtiment Champagne 3 P 30

Abute Nationale 25

F-32151 Le Plessis Addieson

Tai (1) 40 34 38 35

Faz (1) 40 34 38 11

Hational Communities E. J. L. Strand 7 - PHILITY R3 - Mislandhon 1-20089 Reztrand Min Fel (02) 57 50 03 03 (seex 257 547 Fax (07) 57 50 04 30

Harthand Seminoedustrar S. g. A. Via Gel Caravaggia, 107 HGG147 Roma, vet. (CS) 5:12:48:30 Fax (OS) 5:13:79:47 Returned 18 Sax 1009

Grassmandlarvagen 7 S-12123 Johanneshov Tei (08) 7 22 30 50 Fares 10 721

Fax (05) 7 72 30 35

National Someonistics Postrus 30 Nt. 1330 A8 Weess Tel: 10 29 40; I 34 48 Fax (0 29 40) I 34 20

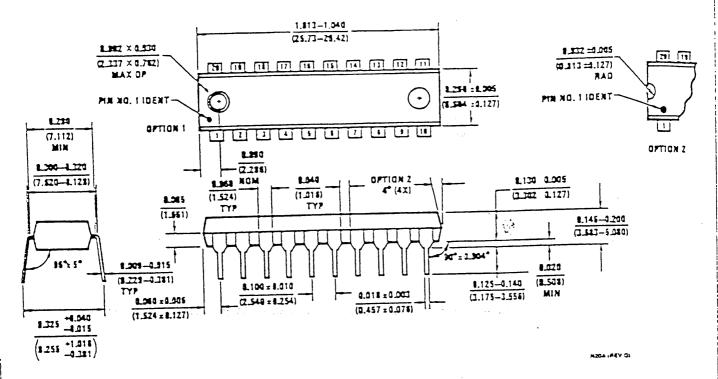

# Physical Dimensions

20-Lead Molded Dual-in-Line (N) Order Number MM57C200/N NS Package Number N20 A