# 8-Bit Microcontroller for Monitor (32K OTP ROM Type)

#### Features

- Operating voltage range: 4.5V to 5.5V

- CMOS technology for low power consumption

- 6502 8-bit CMOS CPU core

- 8 MHz operation frequency

- 32K bytes of OTP (one time programming) ROM

- 512 bytes of RAM

- One 8-bit base timer

- 13 channels of 8-bit PWM outputs with 5V open drain

- 4 channel A/D converters with 6-bit resolution

- 25 bi-directional I/O port pins (8 dedicated I/O pins)

- Hsync/vsync signals processor for separate & composite signal, including hardware sync signals polarity detection and freq. counters with 2 sets of Hsync counting interval

- Hsync/Vsync polarity controlled output, 5 selectable free run output signals and self-test patterns, automute function, half freq. I/O function

- Two built-in I<sup>2</sup>C bus interfaces support VESA DDC1/2B+

#### **General Description**

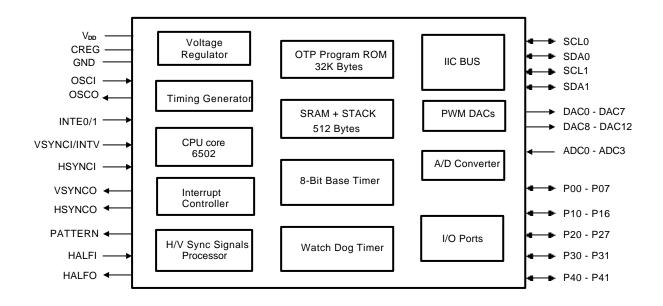

The NT68P62 is a new generation of monitor  $\mu$ C for autosync and digital control applications. Particularly, this chip supports various and efficient functions to allow users to easily develop USB monitors. It contains the 6502 8-bit CPU core, 512 bytes of RAM used as working RAM and stack area, 32K bytes of OTP ROM, 13-channel of 8-bit PWM D/A converters, 4-channel A/D converters for keys detection which can save I/O pins, one 8-bit pre-loadable base timer, internal Hsync and Vsync signals processor, and a watch-dog timer which prevents the system from

- Two layers of interrupt management NMI interrupt sources INTEO (External INT with colorable adaptrized)

- INTE0 (External INT with selectable edge trigger)

INTMUTE (Auto Mute Activated)

- IRQ interrupt sources

- INTS0/1 (SCL Go-low INT)

- INTA0/1 (Slave Address Matched INT)

- INTTX0/1 (Shift Register INT)

- INTRX0/1 (Shift Register INT)

- INTNAK0/1 (No Acknowledge)

- INTSTOP0/1 (Stop Condition Occurred INT)

- INTE1 (External INT with Selectable Edge Trigger)

- INTV (VSYNC INT)

- INTMR (Base Timer INT)

- INTADC (AD Conversion Done INT)

- Hardware watch-dog timer function

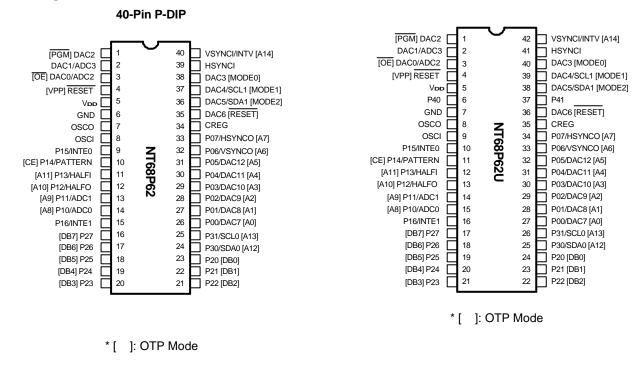

- 40-pin P-DIP and 42-pin S-DIP packages

abnormal operation and two fC bus interface. The user can store EDID data in the 128 bytes of RAM for DDC1/2B, so that user can reduce a dedicated EEPROM for EDID. And Half frequency output function can save external oneshot circuit. All of these designs are committed to offer our user saving component cost. The 42 pin S-DIP IC provides two additional I/O pins – port40 & port41, Part number NT68P62U represents the S-DIP IC. For future reference, port40 & port42 is only available for the 42 pin S-DIP IC.

#### **Pin Configurations**

42-Pin S-DIP

#### **Block Diagram**

### **Pin Description**

| Pin    | No.    | <b>D</b>             | <b>D</b>    |            |                                                                                                                                                                                                                                  |

|--------|--------|----------------------|-------------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 40 Pin | 42 Pin | Designation          | Reset Init. | I/O        | Description                                                                                                                                                                                                                      |

| 1      | 1      | DAC2<br>[PGM]        |             | 0<br>[1]   | Open drain 5V, D/A converter output 2<br>[OTP ROM program control]                                                                                                                                                               |

| 2      | 2      | DAC1/ADC3            | DAC1        | 0          | Open drain 5V, D/A converter output 1, shared with A/D converter channel 3 input                                                                                                                                                 |

| 3      | 3      | DAC0/ADC2            | DAC0        | 0          | Open drain 5V, D/A converter output 0, shared with A/D<br>converter channel 2 input<br>[OTP ROM program output enable]                                                                                                           |

| 4      | 4      | RESET                |             | <br>[P]    | Schmitt Trigger input pin, low active reset with internal pulled down $50K\Omega$ register * [OTP ROM program supply voltage]                                                                                                    |

| 5      | 5      | Vdd                  |             | Р          | Power                                                                                                                                                                                                                            |

| 6      | 7      | GND                  |             | Р          | Ground                                                                                                                                                                                                                           |

| 7      | 8      | OSCO                 |             | 0          | Crystal OSC output                                                                                                                                                                                                               |

| 8      | 9      | OSCI                 |             | I          | Crystal OSC input                                                                                                                                                                                                                |

| 9      | 10     | P15/INTE0            |             | I/O        | Bi-directional I/O pin with internal pulled up $22K\Omega$ register,<br>shared with input pin of external interrupt source0 (NMI),<br>with schmitt trigger, selectable triggered, and internal pulled<br>up $22K\Omega$ register |

| 10     | 11     | P14/PATTERN          |             | I/O        | Bi-directional I/O pin with internal pulled up 22K $\!\Omega$ register, shared with the output of self test pattern                                                                                                              |

|        |        | [ A15/CE ]           |             | [1]        | [OTP ROM program address buffer & chip enable ]                                                                                                                                                                                  |

| 11     | 12     | P13/HALFI<br>[ A11 ] | P13         | I/O<br>[1] | Bi-directional I/O pin with internal pulled up $22K\Omega$ register,<br>shared with half hsync input, shared with A/D converter<br>channel 3 input<br>[ OTP ROM program address buffer ]                                         |

| 12     | 13     | P12/HALFO<br>[ A10 ] | P12         | I/O<br>[1] | Bi-directional I/O pin with internal pulled up $22K\Omega$ register, shared with half hsync output [OTP ROM program address buffer ]                                                                                             |

| 13     | 14     | P11/ADC1<br>[ A9 ]   | P11         | I/O<br>[1] | Bi-directional I/O pin with internal pulled up 22KΩ register,<br>shared with A/D converter channel 1 input<br>[ OTP ROM program address buffer ]                                                                                 |

| 14     | 15     | P10/ADC0<br>[ A8 ]   | P10         | I/O<br>[1] | Bi-directional I/O pin with internal pulled up $22K\Omega$ register, shared with A/D converter channel 0 input [ OTP ROM program address buffer ]                                                                                |

| 15     | 16     | P16/INTE1            | P16         | I/O        | Bi-directional I/O pin with internal pulled up $22K\Omega$ register, shared with input pin of external interrupt source1, with Schmitt Trigger, selectable triggered, and an internal pulled up $22K\Omega$ register             |

### Pin Description (continued)

| Pin     | No.     |                 | <b>D</b>    |          |                                                                                                                         |

|---------|---------|-----------------|-------------|----------|-------------------------------------------------------------------------------------------------------------------------|

| 40 Pin  | 42 Pin  | Designation     | Reset Init. | I/O      | Description                                                                                                             |

| 16 - 23 | 17 - 24 | P27 – P20       |             | I/O      | Bi-directional I/O pin, push-pull structure with high current drive/sink capability                                     |

|         |         | [DB7]-[DB0]     |             | [ I/O ]  | [OTP ROM program data buffer ]                                                                                          |

| 24      | 25      | P30/SDA0        | P30         | I/O      | Open drain 5V bi-directional I/O pin P30, shared with SDA0                                                              |

|         |         | [ A12 ]         |             | [1]      | pin of I <sup>2</sup> C bus Schmitt Trigger buffer<br>[ OTP ROM program address buffer ]                                |

| 25      | 26      | P31/SCL0        | P31         | I/O      | Open drain 5V bi-directional I/O pin P31, shared with SCL0                                                              |

|         |         | [ A13 ]         |             | [1]      | pin of I <sup>2</sup> c bus Schmitt Trigger buffer<br>[ OTP ROM program address buffer ]                                |

| 26      | 27      | P00/DAC7        | P00         | I/O      | Bi-directional I/O pin with internal pulled up $22K\Omega$ register,                                                    |

|         |         | [ A0 ]          |             | [1]      | shared with open drain 5V D/A converter output 8<br>[ OTP ROM program address buffer ]                                  |

| 27      | 28      | P01/DAC8        | P01         | I/O      | Bi-directional I/O pin with internal pulled up $22K\Omega$ register,                                                    |

|         |         | [A1]            |             | [1]      | shared with open drain 5V D/A converter output 9<br>[ OTP ROM program address buffer ]                                  |

| 28      | 29      | P02/DAC9        | P02         | I/O      | Bi-directional I/O pin with internal pulled up $22K\Omega$ register,                                                    |

|         |         | [A2]            |             | [1]      | shared with open drain 5V D/A converter output 10 [ OTP ROM program address buffer ]                                    |

| 29      | 30      | P03/DAC10       | P03         | I/O      | Bi-directional I/O pin with internal pulled up $22K\Omega$ register,                                                    |

|         |         | [ A3 ]          |             | [1]      | shared with open drain 5V D/A converter output 11<br>[OTP ROM program address buffer ]                                  |

| 30      | 31      | P04/DAC11       | P04         | I/O      | Bi-directional I/O pin with internal pulled up $22K\Omega$ register,                                                    |

|         |         | [ A4 ]          |             | [1]      | shared with open drain 5V D/A converter output 12<br>[OTP ROM program address buffer ]                                  |

| 31      | 32      | P05/DAC12       | P05         | I/O      | Bi-directional I/O pin with internal pulled up $22K\Omega$ register,                                                    |

|         |         | [ A5 ]          |             | [1]      | shared with open drain 5V D/A converter output 13<br>[ OTP ROM program address buffer ]                                 |

| 32      | 33      | P06/VSYNCO      | P06         | I/O      | Bi-directional I/O pin with internal pulled up 22K $\Omega$ register, shared with vsync out                             |

|         |         | [ A6 ]          |             | [1]      | [OTP ROM program address buffer ]                                                                                       |

| 33      | 34      | P07/HSYNCO      | P07         | I/O      | Bi-directional I/O pin with internal pulled up $22K\Omega$ register,                                                    |

|         |         | [ A7 ]          |             | [1]      | shared with hsync out<br>[ OTP ROM program address buffer ]                                                             |

| 34      | 35      | CREG            |             | 0        | On chip voltage regulator output, external regulating                                                                   |

|         |         |                 |             |          | cap.(10 $\mu$ F ~ 100 $\mu$ F) should be connected here                                                                 |

| 35      | 36      | DAC6<br>[RESET] |             | 0<br>[1] | Open drain 5V, D/A converter output 6                                                                                   |

|         | 20      |                 |             |          | [OTP ROM reset]                                                                                                         |

| 36      | 38      | DAC5/SDA1       |             | 0        | Open drain 5V, D/A converter output 5, shared with open drain SDA1 line of I <sup>2</sup> C bus, Schmitt Trigger buffer |

|         |         | [ MODE2 ]       |             | [ ]      | [OTP ROM mode select]                                                                                                   |

| <b>Pin Description</b> | (continued) |

|------------------------|-------------|

|------------------------|-------------|

| Pin    | No.    | Designation            | Reset Init. | I/O      | Description                                                                                                                                                                                                                                                                 |

|--------|--------|------------------------|-------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 40 Pin | 42 Pin |                        |             |          |                                                                                                                                                                                                                                                                             |

| 37     | 39     | DAC4/SCL1              |             | 0        | Open drain 5V, D/A converter output 4, shared with open drain SCL1 line of I <sup>2</sup> C bus, Schmitt Trigger buffer                                                                                                                                                     |

|        |        | [ MODE1 ]              |             | [1]      | [OTP ROM mode select]                                                                                                                                                                                                                                                       |

| 38     | 40     | DAC3                   |             | 0        | Open drain 5V, D/A converter output 3                                                                                                                                                                                                                                       |

|        |        | [ MODE0 ]              |             | [1]      | [OTP ROM mode select]                                                                                                                                                                                                                                                       |

| 39     | 41     | HSYNCI                 |             | I        | Debouncing & Schmitt Trigger input pin for video horizontal sync signal, internal pull high, shared with composite sync input                                                                                                                                               |

| 40     | 42     | VSYNCI/INTV<br>[ A14 ] | VSYNCI      | I<br>[1] | Debouncing & Schmitt trigger input pin for video vertical sync signal, internal pull high, shared with input pin of external interrupt source intv with Schmitt Trigger, selectable triggered, and internal pulled up $22K\Omega$ register [OTP ROM program address buffer] |

| -      | 6      | P40                    |             | I/O      | Bi-directional I/O pin with internal pulled up 22K $\!\Omega$ register, only 42 pin S-DIP available                                                                                                                                                                         |

| -      | 37     | P41                    |             | I/O      | Bi-directional I/O pin with internal pulled up 22K $\!\Omega$ register, only 42 pin S-DIP available                                                                                                                                                                         |

\* This RESET pin must be pulled high by external pulled-up register (5KΩ suggestion), or it will remain in low voltage to continually rest system.

#### **Functional Description**

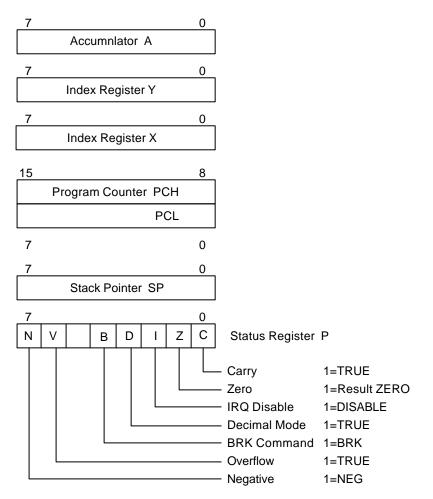

#### 1.6502 CPU

The 6502 is an 8-bit CPU that provides 56 instructions, decimal and binary arithmetic, thirteen addressing modes, true indexing capability, programmable stack pointer and variable length stack, a wide selection of addressable memory ranges, and interrupt input options.

The CPU clock cycle is 4MHz (8MHz system clock divided by 2). Please refer to the 6502 data sheet for more detailed information.

Figure 1.1. The 6502 CPU Registers and Status Flags

### 2. Instruction Set List

| Instruction Code | Meaning                       | Operation                |

|------------------|-------------------------------|--------------------------|

| ADC              | Add with carry                | A + M + C A, C           |

| AND              | Logical AND                   | A M A                    |

| ASL              | Shift left one bit            | C M7M0 0                 |

| BCC              | Branch if carry clears        | Branch on $C = 0$        |

| BCS              | Branch if carry sets          | Branch on C = 1          |

| BEQ              | Branch if equal to zero       | Branch on Z = 1          |

| BIT              | Bit test                      | A M, M7 N, M6 V          |

| BMI              | Branch if minus               | Branch on N = 1          |

| BNE              | Branch if not equal to zero   | Branch on $Z = 0$        |

| BPL              | Branch if plus                | Branch on $N = 0$        |

| BRK              | Break                         | Forced Interrupt PC+2 PC |

| BVC              | Branch if overflow clears     | Branch on V = 0          |

| BVS              | Branch if overflow sets       | Branch on V = 1          |

| CLC              | Clear carry                   | 0 C                      |

| CLD              | Clear decimal mode            | 0 D                      |

| CLI              | Clear interrupt disable bit   | 0 1                      |

| CLV              | Clear overflow                | 0 V                      |

| CMP              | Compare Accumulator to memory | A - M                    |

| СРХ              | Compare with index register X | X - M                    |

| CPY              | Compare with index register Y | Y - M                    |

| DEC              | Decrement memory by one       | M - 1 M                  |

| DEX              | Decrement index X by one      | X - 1 X                  |

| DEY              | Decrement index Y by one      | Y - 1 Y                  |

| EOR              | Logical exclusive-OR          | A M A                    |

| INC              | Increment memory by one       | M + 1 M                  |

| INX              | Increment index X by one      | X + 1 X                  |

| INY              | Increment index Y by one      | Y + 1 Y                  |

### Instruction Set List (continued)

| Instruction Code | Meaning                           | Operation                     |

|------------------|-----------------------------------|-------------------------------|

| JMP              | Jump to new location              | (PC+1) PCL, (PC+2) PCH        |

| JSR              | Jump to subroutine                | PC+2 , (PC+1) PCL, (PC+2) PCH |

| LDA              | Load accumulator with memory      | M A                           |

| LDX              | Load index register X with memory | M X                           |

| LDY              | Load index register Y with memory | M Y                           |

| LSR              | Shift right one bit               | 0 M7M0 C                      |

| NOP              | No operation                      | No operation (2 cycles)       |

| ORA              | Logical OR                        | A+M A                         |

| PHA              | Push accumulator on stack         | A                             |

| PHP              | Push status register on stack     | Р                             |

| PLA              | Pull accumulator from stack       | A                             |

| PLP              | Pull status register from stack   | Р                             |

| ROL              | Rotate left through carry         | C M7M0 C                      |

| ROR              | Rotate right through carry        | C M7M0 C                      |

| RTI              | Return from interrupt             | P, PC                         |

| RTS              | Return from subroutine            | PC , PC+1 PC                  |

| SBC              | Subtract with borrow              | A - M - C A, C                |

| SEC              | Set carry                         | 1 C                           |

| SED              | Set decimal mode                  | 1 D                           |

| SEI              | Set interrupt disable status      | 1 I                           |

| STA              | Store accumulator in memory       | A M                           |

| STX              | Store index register X in memory  | X M                           |

| STY              | Store index register Y in memory  | Y M                           |

| ТАХ              | Transfer accumulator to index X   | A X                           |

| ТАҮ              | Transfer accumulator to index Y   | A Y                           |

| TSX              | Transfer stack pointer to index X | S X                           |

| ТХА              | Transfer index X to accumulator   | ХА                            |

| TXS              | Transfer index X to stack pointer | X S                           |

| TYA              | Transfer index Y to accumulator   | Y A                           |

\* Refer to 6502 programming data book for more details.

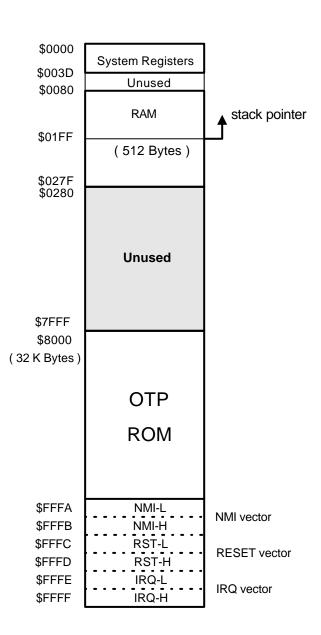

#### 3. RAM: 512 X 8 bits

The built-in 512 X 8-bit SRAM is used for data memory and stack area. The RAM addressing range is from \$0080 to \$027F. The contents of RAM are undetermined at power-up and are not affected by system reset. Software programmers can allocate stack area in the RAM by setting stack pointer register (S). Because the 6502 default stack pointer is \$01FF, programmers must set S register to FFH when starting the program.

| as; | LDX | #\$FF |

|-----|-----|-------|

|     | TXS |       |

#### 4. ROM: 32K X 8 bits

NT68P62 provides 32K ROM space for programming. The ROM space is located from \$8000 to \$FFFF. The addresses, from \$FFFA to \$FFFF, are reserved for the 6502 CPU vectors, thus users must arrange them by themselves.

### 5. System Registers

| Addr.                                           | Register | INIT | Bit7    | Bit6          | Bit5          | Bit4          | Bit3        | Bit2     | Bit1     | Bit0     | R/W |  |

|-------------------------------------------------|----------|------|---------|---------------|---------------|---------------|-------------|----------|----------|----------|-----|--|

|                                                 | •        |      |         | Contro        | I Registers   | for I/O Port0 | & Port1     |          |          |          |     |  |

| \$0000                                          | PT0      | FFH  | P07     | P06           | P05           | P04           | P03         | P02      | P01      | P00      | RW  |  |

| \$0001                                          | PT1      | 7FH  | -       | P16           | P15           | P14           | P13         | P12      | P11      | P10      | RW  |  |

| Control Register to Control Port2 I/O Direction |          |      |         |               |               |               |             |          |          |          |     |  |

| \$0002                                          | PT2DIR   | FFH  | P270E   | P26OE         | P25OE         | P240E         | P23OE       | P22OE    | P210E    | P20OE    | W   |  |

| Control Registers for I/O Port2 - 4             |          |      |         |               |               |               |             |          |          |          |     |  |

| \$0003                                          | PT2      | FFH  | P27     | P26           | P25           | P24           | P23         | P22      | P21      | P20      | RW  |  |

| \$0004                                          | PT3      | 03H  | -       | -             | -             | -             | -           | -        | P31      | P30      | RW  |  |

| \$0005                                          | PT4      | 03H  | 0       | nly available | for the 42 Pi | n SDIP versi  | on          | -        | P41      | P40      | RW  |  |

|                                                 |          |      |         | Cont          | rol Register  | s for Synpro  | cessor      |          |          |          |     |  |

| \$0006                                          | SYNCON   | FFH  | -       | -             | -             | -             | INSEN       | -        | HSEL     | S/ C     | R   |  |

|                                                 |          | FFH  | -       | -             | -             | -             | INSEN       | ENHSEL   | HSEL     | S/C      | W   |  |

| \$0007                                          | HV CON   | FFH  | -       | -             | HSYNCI        | VSYNCI        | HPOLI       | VPOLI    | HPOLO    | VPOLO    | R   |  |

|                                                 |          | FFH  | ENHOUT  | ENHOUT        | -             | -             | -           | -        | HPOLO    | VPOLO    | W   |  |

| \$0008                                          | HCNT L   | 00H  | HCL7    | HCL6          | HCL5          | HCL4          | HCL3        | HCL2     | HCL1     | HCL0     | R   |  |

| \$0009                                          | HCNT H   | 00H  | HCNTOV  | -             | -             | -             | HCH3        | HCH2     | HCH1     | HCH0     | R   |  |

|                                                 |          |      | CLRHOV  | -             | -             | -             | -           | -        | -        | -        | W   |  |

| \$000A                                          | VCNT L   | 00H  | VCL7    | VCL6          | VCL5          | VCL4          | VCL3        | VCL2     | VCL1     | VCL0     | R   |  |

| \$000B                                          | VCNT H   | 00H  | VCNTOV  | -             | VCH5          | VCH4          | VCH3        | VCH2     | VCH1     | VCH0     | R   |  |

|                                                 |          |      | CLRVOV  | -             | -             | -             | -           | -        | -        | -        | W   |  |

| \$000C                                          | FREECON  | FFH  | ENPAT   | PAT1          | -             | -             | -           | FREQ2    | FREQ1    | FREQ0    | W   |  |

| \$000D                                          | HALFCON  | FFH  | ENHALF  | NOHALF        | HALFPOL       | -             | -           | -        | -        | -        | W   |  |

| \$000E                                          | AUTOMUTE | FFH  | ENHDIFF | ENPOL         | ENOVER        | -             | HDIFFVL3    | HDIFFVL2 | HDIFFVL1 | HDIFFVL0 | W   |  |

|                                                 | -        | -    |         | Control Reg   | gisters to En | able PWM 8    | - 15 Channe | ls       |          |          |     |  |

| \$000F                                          | ENDAC    | FFH  | -       | -             | ENDK12        | ENDK11        | ENDK10      | ENDK9    | ENDK8    | ENDK7    | W   |  |

|                                                 |          |      |         | Contro        | Registers for | or ADC 0 - 3  | Channels    |          |          |          |     |  |

| \$0010                                          | ENADC    | FFH  | CSTA    | -             | -             | -             | ENADC3      | ENADC2   | ENADC1   | ENADC0   | W   |  |

| \$0011                                          | AD0 REG  | C0H  | -       | -             | AD05          | AD04          | AD03        | AD02     | AD01     | AD00     | R   |  |

| \$0012                                          | AD1 REG  | 00H  | -       | -             | AD15          | AD14          | AD13        | AD12     | AD11     | AD10     | R   |  |

| \$0013                                          | AD2 REG  | 00H  | -       | -             | AD25          | AD24          | AD23        | AD22     | AD21     | AD20     | R   |  |

| \$0014                                          | AD3 REG  | 00H  | -       | -             | AD35          | AD34          | AD33        | AD32     | AD31     | AD30     | R   |  |

### System Registers (continued)

| Addr.  | Register                              | INIT      | Bit7          | Bit6           | Bit5          | Bit4         | Bit3          | Bit2         | Bit1          | Bit0     | R/W |  |  |

|--------|---------------------------------------|-----------|---------------|----------------|---------------|--------------|---------------|--------------|---------------|----------|-----|--|--|

|        | Control Re                            | egister f | or Polling (F | Read) Interru  | pt Groups     | & Clearing ( | Write) INTE0  | & INTMUTE    | Interrupt Red | quests   |     |  |  |

| \$0016 | NMIPOLL                               | 00H       | -             | -              | -             | -            | -             | -            | INTE0         | INTMUTE  | R   |  |  |

|        |                                       |           | -             | -              | -             | -            | -             | -            | CLRE0         | CLRMUTE  | W   |  |  |

| \$0017 | IRQPOLL                               | 00H       | -             | -              | -             | -            | -             | IRQ2         | IRQ1          | IRQ0     | R   |  |  |

|        | Control Registers of Interrupt Enable |           |               |                |               |              |               |              |               |          |     |  |  |

| \$0018 | IENMI                                 | 00H       | -             | -              | -             | -            | -             | -            | INTE0         | INTMUTE  | RW  |  |  |

| \$0019 | IEIRQ0                                | 00H       | -             | -              | INTS0         | INTA0        | INTTX0        | INTRX0       | INTNAK0       | INTSTOP0 | RW  |  |  |

| \$001A | IEIRQ1                                | 00H       | -             | -              | INTS1         | INTA1        | INTTX1        | INTRX1       | INTNAK1       | INTSTOP1 | RW  |  |  |

| \$001B | IEIRQ2                                | 00H       | -             | -              | -             | -            | INTADC        | INTV         | INTE1         | INTMR    | RW  |  |  |

|        |                                       |           | Control Reg   | jisters for Po | olling (Read) | & Clearing   | (Write) Inter | rupt Request | S             |          |     |  |  |

| \$001C | IRQ0                                  | 00H       | -             | -              | INTS0         | INTA0        | INTTX0        | INTRX0       | INTNAK0       | INTSTOP0 | R   |  |  |

|        |                                       |           | -             | -              | CLRS0         | CLRA0        | CLRTX0        | CLRRX0       | CLRNAK0       | CLRSTOP0 | W   |  |  |

| \$001D | IRQ1                                  | 00H       | -             | -              | INTS1         | INTA1        | INTTX1        | INTRX1       | INTNAK1       | INTSTOP1 | R   |  |  |

|        |                                       |           | -             | -              | CLRS1         | CLRA1        | CLRTX1        | CLRRX1       | CLRNAK1       | CLRSTOP1 | W   |  |  |

| \$001E | IRQ2                                  | 00H       | -             | -              | -             | -            | INTADC        | INTV         | INTE1         | INTMR    | R   |  |  |

|        |                                       |           | -             | -              | -             | -            | CLRADC        | CLRV         | CLRE1         | CLRMR    | W   |  |  |

|        |                                       |           | Sele          | ction of Edg   | e Triggered   | for INTV, IN | TE0 & 1 Inte  | rrupts       |               |          |     |  |  |

| \$001F | TRIGGER                               | FFH       | -             | -              | -             | -            | -             | INTVR        | INTE1R        | INTE0R   | R/W |  |  |

|        |                                       |           |               | Control Re     | gisters for C | learing Wat  | ch Dog Time   | er           |               |          |     |  |  |

| \$0020 | CLR WDT                               | -         | 0             | 1              | 0             | 1            | 0             | 1            | 0             | 1        | W   |  |  |

|        |                                       |           |               | Control F      | Register for  | DDC1/2B+ o   | f Channel 0   |              |               |          |     |  |  |

| \$0021 | CH0ADDR                               | A0H       | ADR7          | ADR6           | ADR5          | ADR4         | ADR3          | ADR2         | ADR1          | -        | W   |  |  |

| \$0022 | CH0TXDAT                              | 00H       | TX7           | TX6            | TX5           | TX4          | TX3           | TX2          | TX1           | TX0      | W   |  |  |

| \$0023 | CHORXDAT                              | 00H       | RX7           | RX6            | RX5           | RX4          | RX3           | RX2          | RX1           | RX0      | R   |  |  |

| \$0024 | CH0CON                                | E0H       | ENDDC         | MD1/2          | -             | START        | STOP          | -            | TXACK         | -        | W   |  |  |

|        |                                       |           | -             | -              | SRW           | START        | STOP          | -            | -             | -        | R   |  |  |

| \$0025 | CH0CLK                                | FFH       | MODE          | MRW            | RSTART        | -            | -             | DDC2BR2      | DDC2BR1       | DDC2BR0  | W   |  |  |

|        |                                       |           |               | Control F      | Register for  | DDC1/2B+ o   | f Channel 1   |              |               |          |     |  |  |

| \$0026 | CH1ADDR                               | A0H       | ADR7          | ADR6           | ADR5          | ADR4         | ADR3          | ADR2         | ADR1          | -        | W   |  |  |

| \$0027 | CH1TXDAT                              | 00H       | TX7           | TX6            | TX5           | TX4          | TX3           | TX2          | TX1           | TX0      | W   |  |  |

| \$0028 | CH1RXDAT                              | 00H       | RX7           | RX6            | RX5           | RX4          | RX3           | RX2          | RX1           | RX0      | R   |  |  |

### System Registers (continued)

| Addr.                            | Register | INIT | Bit7  | Bit6    | Bit5        | Bit4       | Bit3         | Bit2    | Bit1    | Bit0    | R/W |  |

|----------------------------------|----------|------|-------|---------|-------------|------------|--------------|---------|---------|---------|-----|--|

| \$0029                           | CH1CON   | E0H  | ENDDC | MD1/2   | -           | START      | STOP         | -       | TXACK   | -       | W   |  |

|                                  |          |      | -     | -       | SRW         | START      | STOP         | -       | -       | -       | R   |  |

| \$002A                           | CH1CLK   | FFH  | MODE  | MRW     | RSTART      | -          | -            | DDC2BR2 | DDC2BR1 | DDC2BR0 | W   |  |

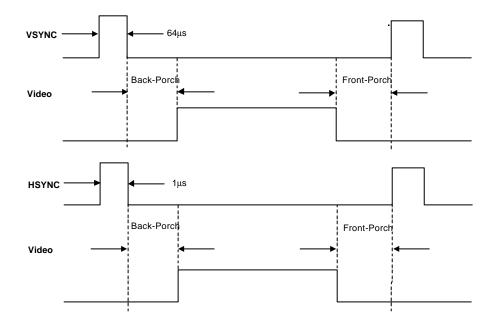

| Control Registers for Base Timer |          |      |       |         |             |            |              |         |         |         |     |  |

| \$002E                           | BT       | 00H  | BT7   | BT6     | BT5         | BT4        | BT3          | BT2     | BT1     | BT0     | W   |  |

| \$002F                           | BTCON    | 03H  | -     | -       | -           | -          | -            | -       | BTCLK   | ENBT    | W   |  |

|                                  |          |      |       | Control | Registers f | or PWM Cha | innel 0 - 13 | •       |         |         |     |  |

| \$0030                           | DACH0    | 80H  | DKVL7 | DKVL6   | DKVL5       | DKVL4      | DKVL3        | DKVL2   | DKVL1   | DKVL0   | RW  |  |

| \$0031                           | DACH1    | 80H  | DKVL7 | DKVL6   | DKVL5       | DKVL4      | DKVL3        | DKVL2   | DKVL1   | DKVL0   | RW  |  |

| \$0032                           | DACH2    | 80H  | DKVL7 | DKVL6   | DKVL5       | DKVL4      | DKVL3        | DKVL2   | DKVL1   | DKVL0   | RW  |  |

| \$0033                           | DACH3    | 80H  | DKVL7 | DKVL6   | DKVL5       | DKVL4      | DKVL3        | DKVL2   | DKVL1   | DKVL0   | RW  |  |

| \$0034                           | DACH4    | 80H  | DKVL7 | DKVL6   | DKVL5       | DKVL4      | DKVL3        | DKVL2   | DKVL1   | DKVL0   | RW  |  |

| \$0035                           | DACH5    | 80H  | DKVL7 | DKVL6   | DKVL5       | DKVL4      | DKVL3        | DKVL2   | DKVL1   | DKVL0   | RW  |  |

| \$0036                           | DACH6    | 80H  | DKVL7 | DKVL6   | DKVL5       | DKVL4      | DKVL3        | DKVL2   | DKVL1   | DKVL0   | RW  |  |

| \$0037                           |          | -    | -     | -       | -           | -          | -            | -       | -       | -       |     |  |

| \$0038                           | DACH7    | 80H  | DKVL7 | DKVL6   | DKVL5       | DKVL4      | DKVL3        | DKVL2   | DKVL1   | DKVL0   | RW  |  |

| \$0039                           | DACH8    | 80H  | DKVL7 | DKVL6   | DKVL5       | DKVL4      | DKVL3        | DKVL2   | DKVL1   | DKVL0   | RW  |  |

| \$003A                           | DACH9    | 80H  | DKVL7 | DKVL6   | DKVL5       | DKVL4      | DKVL3        | DKVL2   | DKVL1   | DKVL0   | RW  |  |

| \$003B                           | DACH10   | 80H  | DKVL7 | DKVL6   | DKVL5       | DKVL4      | DKVL3        | DKVL2   | DKVL1   | DKVL0   | RW  |  |

| \$003C                           | DACH11   | 80H  | DKVL7 | DKVL6   | DKVL5       | DKVL4      | DKVL3        | DKVL2   | DKVL1   | DKVL0   | RW  |  |

| \$003D                           | DACH12   | 80H  | DKVL7 | DKVL6   | DKVL5       | DKVL4      | DKVL3        | DKVL2   | DKVL1   | DKVL0   | RW  |  |

#### 6. Timing Generator

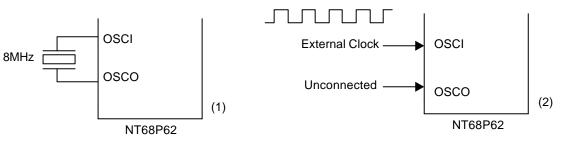

This block generates the system timing and control signal to be supplied to the CPU and on-chip peripherals. A crystal quartz, ceramic resonator, or an external clock signal which will be provided to the OSCI pin generates system timing. It generates 8MHz system clock, 4MHz for the CPU. Although internal circuits have a feedback resister and compacitor included, users can externally add these components for proper operating.

The typical clock frequency is 8MHz. Different frequencies will affect the operation of those on-chip peripherals whose operating frequency is based on the system clock.

Figure 6.1. Oscillator Connections

#### 7. RESET

The NT68P62 can be reset by the external reset pin or by the internal watch-dog timer. This is used to reset or start the microcontroller from a POWER DOWN condition. During the time that this reset pin is held LOW (\*reset line must be held LOW for at least two CPU clock cycles), writing to or from the  $\mu$ C is inhibited. When a positive edge is detected on the RESET input, the  $\mu$ C will immediately begin the reset sequence.

After a system initialization time of six CPU clock cycles, the mask interrupt flag will be set and the  $\mu$ C will load the program counter from the memory vector locations \$FFFC and \$FFFD. This is the start location for program control.

An internal Schmitt Trigger buffer at the RESET pin is provided to improve noise immunity.

The reset status is as follows:

- 1. PORT0、PORT1、PORT2、PORT3 (& PORT4) pins will act as I/O ports with HIGH output

- 2. Sync processor counters reset and VCNT | HCNT latches cleared

- 3. All sync outputs are disabled

- 4. Base timer is disabled and cleared

- 5. Various Interrupt sources are disabled and cleared

- 6. A/D converter is disabled and stopped

- 7. DDC1/2B+ function is disabled

- 8. PWM DAC0 DAC6 output 50% duty waveform and DAC7 DAC12 is disabled

- 9. Watch-dog timer is cleared and enabled

#### 8. A/D Converters

The structure of these analog to digital converters is 6-bit successive approximation. Analog voltage is supplied from external sources to the A/D input pins and the result of the conversion is stored in the 6-bit data latch registers (\$0011 & \$0014). The A/D channels are activated by clearing the correspondent control bits in the ENADC control register. When users write '0' into one of the enable control bits, its correspondent I/O pin or DAC will be switched to the A/D converter input pin (ADC0 & ADC1 shared with PORT10 & PORT 11; ADC2 & ADC3 shared wit DAC0 & DAC1). Conversion will be started by clearing CSTA bit

(CONVERSION START) in the ENADC control register. When conversion is finished, system will set this INTADC bit. Users can monitor this bit to get the valid A/D conversion data in the AD latch registers (\$0011 - \$0014). Users can also open interrupt sources to remind users to get the stable digital data. Notice that only at the activated A/D channel, its latched data are available.

The analog voltage to be measured should be stabled during the conversion operation and the variation will not exceed LSB for the best accuracy in measurement.

| Addr.  | Register | INIT | Bit7 | Bit6 | Bit5 | Bit4 | Bit3   | Bit2   | Bit1   | Bit0   | R/W |

|--------|----------|------|------|------|------|------|--------|--------|--------|--------|-----|

| \$0010 | ENADC    | FFH  | CSTA | -    | -    | -    | ENADC3 | ENADC2 | ENADC1 | ENADC0 | W   |

| \$0011 | AD0 REG  | COH  | -    | -    | AD05 | AD04 | AD03   | AD02   | AD01   | AD00   | R   |

| \$0012 | AD1 REG  | 00H  | -    | -    | AD15 | AD14 | AD13   | AD12   | AD11   | AD10   | R   |

| \$0013 | AD2 REG  | 00H  | -    | -    | AD25 | AD24 | AD23   | AD22   | AD21   | AD20   | R   |

| \$0014 | AD3 REG  | 00H  | -    | -    | AD35 | AD34 | AD33   | AD32   | AD31   | AD30   | R   |

| \$001B | IEIRQ2   | 00H  | -    | -    | -    | -    | INTADC | INTV   | INTE1  | INTMR  | R/W |

| \$001E | IRQ2     | 00H  | -    | -    | -    | -    | INTADC | INTV   | INTE1  | INTMR  | R   |

|        |          |      | -    | -    | -    | -    | CLRADC | CLRV   | CLRE1  | CLRMR  | W   |

### Reference ADC Table ( $V_{DD} = 5.0V$ )

| 15 | 1.50V | 1C | 2.06V | 23 | 2.59V | 2A | 3.14V |

|----|-------|----|-------|----|-------|----|-------|

| 16 | 1.58V | 1D | 2.12V | 24 | 2.67V | 2B | 3.22V |

| 17 | 1.66V | 1E | 2.20V | 25 | 2.75V | 2C | 3.30V |

| 18 | 1.74V | 1F | 2.28V | 26 | 2.82V | 2D | 3.38V |

| 19 | 1.82V | 20 | 2.35V | 27 | 2.91V | 2E | 3.46V |

| 1A | 1.90V | 21 | 2.44V | 28 | 2.98V | 2F | 3.54V |

| 1B | 1.98V | 22 | 2.51V | 29 | 3.07V | 30 | 3.62V |

Note: It is strongly recommended that the ADC s input signal should be allocated in the ADC s linear voltage range (1.5V~3.5V) to obtain a stable digital value. Do not use the outer ranges (0V~1.4V & 3.6V~5.0V) in which the converted digital value is not guaranteed.

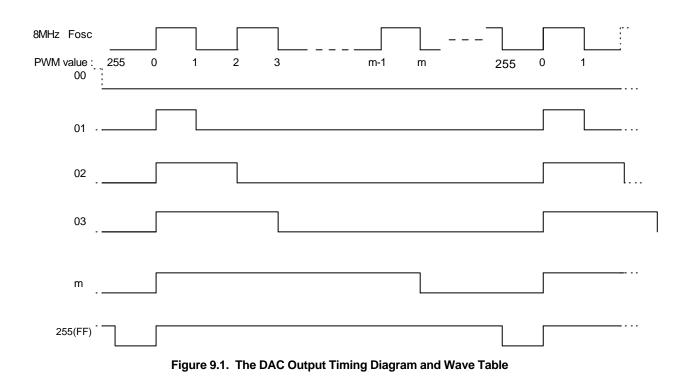

#### 9. PWM DACs (Pulse Width Modulation D/A Converters)

There are 13 PWM D/A converters with 8-bit resolution in NT68P62. All of these D/A (DAC0 - DAC12) converters are opendrain output structure with external 5V applied maximum. DAC0 – DAC6 are dedicated PWM channels, and DAC7 - DAC12 are shared with I/O pins. Those shared PWM channels are activated by clearing the correspondent control bits in the ENDAC control register (\$000F). When users write '0' into one of the enable control bits, its correspondent I/O pin will be switched to PWM output pin.

The PWM refresh rate is 62.5KHz operating on 8MHz system clock. There are 13 readable DACH registers corresponding to 13 PWM channels (\$0030 - \$003D). Each PWM output pulse width is programmable by setting the 8 bit digital to the corresponding DACH registers. When these DACH registers are set to 00H, the DAC will output LOW (GND level) and every 1 bit addition will add 62.5ns pulse width. After reset, all DAC outputs are set to 80H (1/2 duty output). (Please refer to Figure 9.1 for the detailed timing diagram of PWM D/A output.)

#### PWM DACs (continued)

DAC0 & DAC1 are shared with ADC2 & ADC3 input pins respectively. If ENADC2/ $\overline{3}$  bit in the ENADC control register is cleared to LOW, A/D converters will activate simultaneously. After the chip is reset, ENADC2/ $\overline{3}$  bits will be in HIGH state and DAC0 & DAC1 will act as PWM output pins.

DAC4 & DAC5 are shared with SCL1 & SDA1 I/O pins respectively. If users clear the ENDDC bit in the CH1CON control register to LOW, channel 1 of DDC will be activated. When used as DDC channel, the I/O port will be an open drain structure

and include 'Schmitt Trigger' buffer for noise immunity. After the chip is reset, ENDDC bits will be in HIGH state and DAC4 - DAC5 will act as PWM output pins.

| Addr.  | Register | INIT | Bit7  | Bit6  | Bit5   | Bit4   | Bit3   | Bit2   | Bit1   | Bit0   | R/W |

|--------|----------|------|-------|-------|--------|--------|--------|--------|--------|--------|-----|

| \$000F | ENDAC    | FFH  | -     | -     | ENDK12 | ENDK11 | ENDK10 | ENDK9  | ENDK8  | ENDK7  | W   |

| \$0010 | ENADC    | FFH  | CSTA  | -     | -      | -      | ENADC3 | ENADC2 | ENADC1 | ENADC0 | W   |

| \$0030 | DACH0    | 80H  | DKVL7 | DKVL6 | DKVL5  | DKVL4  | DKVL3  | DKVL2  | DKVL1  | DKVL0  | RW  |

| \$0031 | DACH1    | 80H  | DKVL7 | DKVL6 | DKVL5  | DKVL4  | DKVL3  | DKVL2  | DKVL1  | DKVL0  | RW  |

| \$0032 | DACH2    | 80H  | DKVL7 | DKVL6 | DKVL5  | DKVL4  | DKVL3  | DKVL2  | DKVL1  | DKVL0  | RW  |

| \$0033 | DACH3    | 80H  | DKVL7 | DKVL6 | DKVL5  | DKVL4  | DKVL3  | DKVL2  | DKVL1  | DKVL0  | RW  |

| \$0034 | DACH4    | 80H  | DKVL7 | DKVL6 | DKVL5  | DKVL4  | DKVL3  | DKVL2  | DKVL1  | DKVL0  | RW  |

| \$0035 | DACH5    | 80H  | DKVL7 | DKVL6 | DKVL5  | DKVL4  | DKVL3  | DKVL2  | DKVL1  | DKVL0  | RW  |

| \$0036 | DACH6    | 80H  | DKVL7 | DKVL6 | DKVL5  | DKVL4  | DKVL3  | DKVL2  | DKVL1  | DKVL0  | RW  |

| \$0037 |          | -    | -     | -     | -      | -      | -      | -      | -      | -      |     |

| \$0038 | DACH7    | 80H  | DKVL7 | DKVL6 | DKVL5  | DKVL4  | DKVL3  | DKVL2  | DKVL1  | DKVL0  | RW  |

| \$0039 | DACH8    | 80H  | DKVL7 | DKVL6 | DKVL5  | DKVL4  | DKVL3  | DKVL2  | DKVL1  | DKVL0  | RW  |

| \$003A | DACH9    | 80H  | DKVL7 | DKVL6 | DKVL5  | DKVL4  | DKVL3  | DKVL2  | DKVL1  | DKVL0  | RW  |

| \$003B | DACH10   | 80H  | DKVL7 | DKVL6 | DKVL5  | DKVL4  | DKVL3  | DKVL2  | DKVL1  | DKVL0  | RW  |

| \$003C | DACH11   | 80H  | DKVL7 | DKVL6 | DKVL5  | DKVL4  | DKVL3  | DKVL2  | DKVL1  | DKVL0  | RW  |

| \$003D | DACH12   | 80H  | DKVL7 | DKVL6 | DKVL5  | DKVL4  | DKVL3  | DKVL2  | DKVL1  | DKVL0  | RW  |

DAC control register (\$000F) and DAC value register (\$0030 - \$003D)

#### 10. Watch-Dog Timer (WDT)

The NT68P62 implements a watch-dog timer reset to avoid system stop or malfunction. The clock of the WDT is from on-chip RC oscillator which does not require any external components. Thus, the WDT will run, even if the clock on the OSCI/OSCO pins of the device have been stopped. The WDT time interval is about 0.5 second. The WDT must be cleared within every 0.5 second when the software is in normal sequence, otherwise the WDT will overflow and cause a reset. The WDT is cleared and enabled after the system is reset, and can not be disabled by the software. Users can clear the WDT by writing 55H to CLRWDT register (\$0020).

| as; | LDA | #\$55  |

|-----|-----|--------|

|     | STA | \$0020 |

| Addr.  | Register | INIT | Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 | R/W |

|--------|----------|------|------|------|------|------|------|------|------|------|-----|

| \$0020 | CLR WDT  | -    | 0    | 1    | 0    | 1    | 0    | 1    | 0    | 1    | W   |

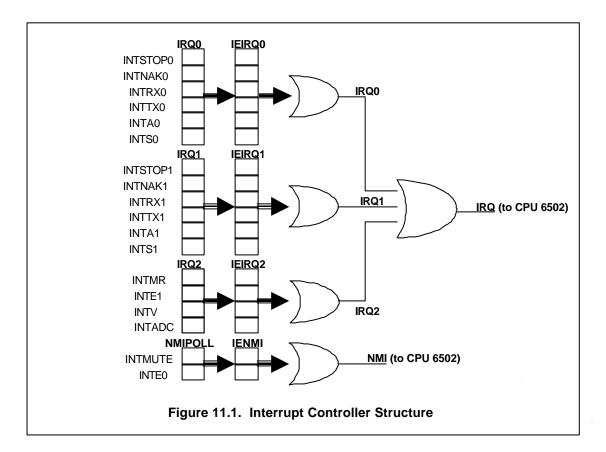

#### **11. Interrupt Controller**

The system provides two kinds of interrupt sources: NMI & IRQ. The NMI can not be masked and if enabling NMI interrupt sources, users will execute the NMI interrupt vector anytime when sources are activated. The IRQ interrupts can be masked by executing a CLI instruction or setting the interrupt mask flag directly in the  $\mu$ C status register. In process IRQ interrupt, if the interrupt mask flag is not set, the  $\mu$ C will begin an interrupt sequence. The program counter and processor status register will be stored in the stack. The µC will then set the interrupt mask flag HIGH so that no further interrupts may occur. At the end of this cycle, the program counter will be loaded from addresses \$FFFE & \$FFFF, then transferring program control to the memory vector located at these addresses. For NMI interrupt,  $\mu C$  will transfer execution sequence to the memory vector located at addresses \$FFFA & \$FFFB.

When manipulating various interrupt sources, NT68P62 divides them into two groups for accessing them easily. One is NMI group and the other is IRQ group.

- The NMI group includes INTE0, INTMUTE.

- The IRQ group includes subgroup of IRQ0, IRQ1, RQ2: IRQ0: DDC1/2B+ Channel 0 interrupt sources; It includes INTS0, INTA0, INTTX0, INTRX0, INTNAK0 and INTSTOP0 interrupts.

- IRQ1: DDC1/2B+ Channel 1 interrupt sources; It includes INTS0, INTA1, INTTX1, INTRX1, INTNAK1 and INTSTOP1.

- IRQ2: It includes INTADC, INTV, INTE1 and INTMR interrupt sources.

Below are the interrupt sources.

| Interrupt | Meaning        | Action                                                                                                                                               |

|-----------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| INTE0 INT | External 0 INT | It will be activated by the rising edge or falling edge of external interrupt pulse.<br>The triggered edge can be selected by EDGE0 bit.             |

| INTMUTE   | Auto Mute      | It will be activated when the mute condition occurres (Hsync frequency change). Please refer the synprocessor section for more detailed explanation. |

#### Maskable Interrupt Group:

Nonmaskable Interrupt Group:

| Interrupt | Meaning               | Action                                                                                                                                   |

|-----------|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------|

| INTADC    | A/D Converion<br>Done | User activates the ADC by clearing the $\overrightarrow{\text{CSTART}}$ bit. When AD conversion is done, this bit will be set.           |

| INTV INT  | Vsync INT             | It will be activated as the rising edge of every vsync pulse.                                                                            |

| INTE1 INT | External 1 INT        | It will be activated by the rising edge or falling edge of external interrupt pulse.<br>The triggered edge can be selected by EDGE1 bit. |

| INTMR INT | Timer INT             | It will be activated as the rising edge of every when the Base Timer counter overflows and counting from \$FF to \$00.                   |

### DDC Channel 0/1 Maskable Interrupt Sources:

| Interrupt   | Meaning                          | Action                                                                                                                                                                                                                                                             |

|-------------|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| INTS INT    | SCL Go-Low INT                   | In DDC1 mode, it will be activated when the external device proceed a DDC2 communication. This action includes pull the SCL line to ground or send out an 'START' condition directly. System will respond to this action by changing DDC1 mode to DDC2 slave mode. |

| INTA INT    | Address Matched<br>INT           | It will be activated at DDC2 slave mode when the external device call NT68P62 slave address. If this calling address matches the NT68P62 address, system will generate this interrupt to remind user                                                               |

| INTTX INT   | Transfer Buffer<br>Empty INT     | It will be activated at DDC2 mode when transmission buffer, IIC_TXDAT, is empty at transmission mode.                                                                                                                                                              |

| INTRX INT   | Receiving Buffer<br>Overflow INT | It will be activated at DDC2 mode when new data have store in the IIC_RXDAT register at receive mode.                                                                                                                                                              |

| INTNAK INT  | No Acknowledge<br>INT            | At transmission mode, this interrupt will be activated when NT68P62 have<br>send out one byte data but the external device does not respond an<br>acknowledge bit to it.                                                                                           |

| INTSTOP INT | DDC2 Stop INT                    | In SLAVE mode, this interrupt will be activated when the NT68P62 receives an 'STOP' condition.                                                                                                                                                                     |

Enabling Interrupts: The system will disable all of these interrupts after reset. Users can enable each of the interrupts by setting the interrupt enable bits at IENMI, IEIRQ0 - IEIRQ3 control registers. For example, if users want to enable external interrupt 0 (INTE0), write '1' to INTE0 bit in the IENMI control register. At the INTE0 pin, whenever NT68P62 has detected an interrupt message, it will generate an interrupt sequence to fetch the NMI vector. Because these IEX control registers can be read, users can read back what interrupts he has been activated. At polling sequence, users need not poll those unactivated interrupts.

Requesting Interrupts to be set: No matter user have been set the interrupt enable bits or not, if the interrupt triggered condition is matched, system will set the correspondent bits in the IRQ0 - IRQ3 control registers or in the NMIPOLL control register (INTE0 & INTMUTE bits). For example, if at VSYNCI pin, system have detected a pulse occurring, system will set the INTV bit in the IRQ2 control register.

Interrupt Groups: System divides IRQ interrupt sources into several groups, ex IRQ0, IRQ1, IRQ2 and IRQ3. At each of these groups, if its membership in the one of the interrupt groups have been activated, its group bit in the IRQPOLL control register will be set. For example, if the INTS0 of the first DDC1/2B+ channel is activated, the INTS0 bit in the IRQ0 will be set and the IRQ0 bit in the IRQPOLL control register also will be set. Notice that the IRQ0 bit will be cleared by system when all of its membership of interrupt sources, INTS0, INTTX0, INTRX0, INTNAK0 and INTSTOP0 have been cleared by the user or system. The NMI group is also oprating the same procedure as IRQ groups. Polling Interrupts: When NMI interrupt occurrs, at NMI interrupt service routine, users must poll the INTE0 & INTMUTE bit in the NMIPOLL control register to confirm the NMI interrupt source. The polling sequence decides the priority of NMI interrupt acceptation. When IRQ interrupt occurrs, at IRQ interrupt service routine, users must poll the IRQ0 - IRQ3 in the IRQPOLL control register to confirm the IRQ interrupt source. In the same way, the polling sequence decides the priority of IRQ interrupt acception. When deciding the IRQ source, users can further confirm the real interrupt source by polling the Correspondent IRQX control register (\$001C - \$001E).

Clearing the Interrupt Request bit: When interrupt occurrs, the CPU will jump to the address defined by the interrupt vector to execute interrupt service routine. Users can check which one of the interrupt sources is activated and operating a tast. It is that upon entering the interrupt service routine, the request bit that caused the interrupt must be cleared by user before finishing the service routine and returning to normal instruction sequence. If users forget to clear this request bit, after returning to main program, it will interrupt CPU again because the request bit remains activated. Simply, users just need write '1' to the polling bits in the NMIPOLL & IRQX registers (\$0016 & \$001C - \$001E) to clear those completed interrupt sources.

Selecting interrupt triggered edge: At INTV, INTE0 & INTE1 interrupt sources, these are now edge triggered type. System provides the selection of rising or falling edge triggered under user's control. After reset, the rising edge triggered are provided and the content is 'FF' in the TRIGGER control register (\$001F). User just clear control bits in this TRIGGER register and switch these interrupts to falling edge triggered.

### **Control Bit Description**

| Addr.  | Register | INIT | Bit7       | Bit6        | Bit5        | Bit4          | Bit3          | Bit2        | Bit1    | Bit0     | R/W |

|--------|----------|------|------------|-------------|-------------|---------------|---------------|-------------|---------|----------|-----|

|        |          |      |            | Cont        | rol Registe | r for Polli   | ng Interrupt  |             |         | •        |     |

| \$0016 | NMIPOLL  | 00H  | -          | -           | -           | -             | -             | -           | INTE0   | INTMUTE  | R   |

|        |          |      | -          | -           | -           | -             | -             | -           | CLRE0   | CLRMUTE  | W   |

| \$0017 | IRQPOLL  | 00H  | -          | -           | -           | -             | -             | IRQ2        | IRQ1    | IRQ0     | R   |

|        |          |      |            | Cont        | rol Registe | ers of Interr | upt Enable    |             |         |          |     |

| \$0018 | IENMI    | 00H  | -          | -           | -           | -             | -             | -           | INTE0   | INTMUTE  | RW  |

| \$0019 | IEIRQ0   | 00H  | -          | -           | INTS0       | INTA0         | INTTX0        | INTRX0      | INTNAK0 | INTSTOP0 | RW  |

| \$001A | IEIRQ1   | 00H  | -          | -           | INTS1       | INTA1         | INTTX1        | INTRX1      | INTNAK1 | INTSTOP1 | RW  |

| \$001B | IEIRQ2   | 00H  | -          | -           | -           | -             | INTADC        | INTV        | INTE1   | INTMR    | RW  |

|        |          | Con  | trol Regis | ters for Po | olling (Rea | d) & Clear    | ing (Write) I | nterrupt Re | quests  |          |     |

| \$001C | IRQ0     | 00H  | -          | -           | INTS0       | INTA0         | INTTX0        | INTRX0      | INTNAK0 | INTSTOP0 | R   |

|        |          |      | -          | -           | CLRS0       | CLRA0         | CLRTX0        | CLRRX0      | CLRNAK0 | CLRSTOP0 | W   |

| \$001D | IRQ1     | 00H  | -          | -           | INTS1       | INTA1         | INTTX1        | INTRX1      | INTNAK1 | INTSTOP1 | R   |

|        |          |      | -          | -           | CLRS1       | CLRA1         | CLRTX1        | CLRRX1      | CLRNAK1 | CLRSTOP1 | W   |

|        |          |      | -          | -           | -           | -             | CLRADC        | CLRV        | CLRE1   | CLRMR    | W   |

|        |          |      | Se         | lection of  | Edge Trig   | gered for I   | NTE0 & 1 Ir   | nterrupt    |         |          |     |

| \$001F | TRIGGER  | FFH  | -          | -           | -           | -             | -             | INTVR       | INTE1R  | INTE0R   | R/W |

#### 12. I/O PORTs

The NT68P62 has 25 pins dedicated to input and output. These pins are grouped into 4 ports.

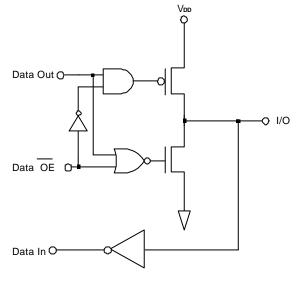

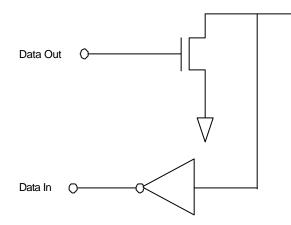

#### 12.1. PORT0: P00 - P07

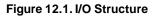

PORT0 is an 8-bit bi-directional CMOS I/O port with PMOS as internal pull-up (Figure 12.1). Each pin of PORT0 may be bit programmed as an input or output port without software control the data direction register. When PORT0 works as output, the data to be output are latched to the port data register and output to the pin. PORT0 pins that have '1's written to them are pulled HIGH by the internal PMOS pull-ups. In this state they can be used as input, then the input signal can be read. This port output is HIGH after reset.

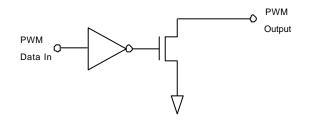

P00 - P05 are shared with DAC7 - DAC12 respectively. If  $\overline{\text{ENDK7}}$  -  $\overline{\text{ENDK12}}$  is set to LOW in ENDAC register, P00 - P05 will act as DAC7 - DAC12 respectively (Figure 12.2). After the chip is reset,  $\overline{\text{ENDK7}}$  -  $\overline{\text{ENDK12}}$  will be in the HIGH state and P00 - P05s will act as I/O ports.

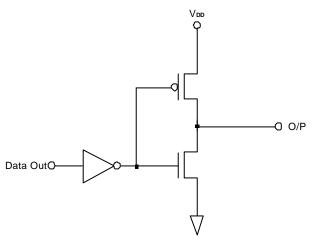

P06、P07 are shared with VSYNCO & HSYNCO respectively. If ENHOUT、ENVOUT is set to LOW in HVCON register, P06、P07 will act as VSYNCO & HSYNCO respectively (Figure 12.3). After the chip is reset,

ENHOUT & ENVOUT will be in the HIGH state and P06、P07 will act as I/O pins.

| Addr.  | Register | INIT | Bit7   | Bit6   | Bit5   | Bit4   | Bit3   | Bit2  | Bit1  | Bit0  | R/W |

|--------|----------|------|--------|--------|--------|--------|--------|-------|-------|-------|-----|

| \$0000 | PT0      | FFH  | P07    | P06    | P05    | P04    | P03    | P02   | P01   | P00   | RW  |

| \$0007 | HV CON   | FFH  | -      | -      | HSYNCI | VSYNCI | HPOLI  | VPOLI | HPOLO | VPOLO | R   |

|        |          | FFH  | ENHOUT | ENVOUT | -      | -      | -      | -     | HPOLO | VPOLO | W   |

| \$000F | ENDAC    | FFH  | -      | -      | ENDK12 | ENDK11 | ENDK10 | ENDK9 | ENDK8 | ENDK7 | W   |

#### Figure 12.2. PWM Output Structure

Figure 12.3. Output Structure

#### 12.2. Port1: P10 - P16

PORT10 - PORT16 is a 7-bit bi-directional CMOS I/O port with PMOS as internal pull-up (Figure 12.1). Each bidirectional I/O pin may be bit programmed as an input or output port without software control the data direction register. When PORT1 works as output, the data to be output is latched to the port data register and output to the pin. PORT1 pins that have '1's written to them are pulled HIGH by the internal PMOS pull-ups. In this state they can be used as input, then the input signal can be read. This port output HIGH after reset.

P10 & P11 are shared with AD0 & AD1 input pins respectively. If the ENADC0/1 bit in the ENADC control register is cleared to LOW, A/D converters will activate simultaneously. After the chip is reset, ENADC0/1 bits will be in the HIGH state and P10 - P11 will act as I/O pins.

P12、P13 are shared with HALF SIGNALS input and OUTPUT pins by accessing the OUTCON control register.

If the ENHALF bit is cleared to LOW, P13 will switch to HALFHI pin (input pin) and P12 will switch to HALFHO pin (output pin, Figure 12.3). For HALFHI & HALFHO pin description, please refer half frequency function in the H/V

sync processor paragraph. After the chip is reset, the  $\overline{\text{ENHALF}}$  bits will be in HIGH state and P12、P13 will act as I/O pins.

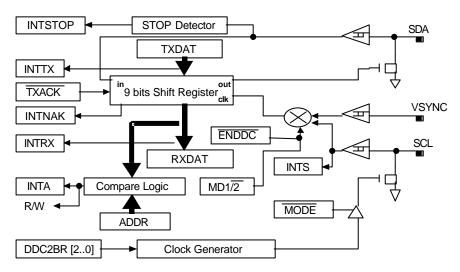

P14 is shared with output pin of self test pattern. If users

clear the PATTERN bit in the SYNCON control register and the free running function has been activated, the P14 will switch to output pin of the self test pattern. This pattern output pin is push-pull structure. After the chip is reset,

PATTERN bits will be in the HIGH state and P14 will act as I/O pin. (Refer the 'Syncprocessor' section for more detailed information.)

P15 & P16 can be shared with external interrupt INTE0 & INTE1 pins if the INTE0/1 bits are set in the control register of interrupt enable (\$0016 & \$0019). These interrupt pin have 'Schmitt Trigger' input buffers. After the chip is reset, INTE0/1 bits will be in HIGH state and P15 & P16 will act as I/O pin.

Refer 'INTERRUPT CONTROLLER' paragraph above for more details about the interrupt function.

| Addr.  | Register | INIT | Bit7  | Bit6 | Bit5 | Bit4 | Bit3   | Bit2   | Bit1   | Bit0    | R/W |

|--------|----------|------|-------|------|------|------|--------|--------|--------|---------|-----|

| \$0001 | PT1      | 7FH  | -     | P16  | P15  | P14  | P13    | P12    | P11    | P10     | RW  |

| \$000C | FREECON  | FFH  | ENPAT | PAT0 | -    | -    | -      | FREQ2  | FREQ1  | FREQ0   | W   |

| \$0010 | ENADC    | FFH  | CSTA  | -    | -    | -    | ENADC3 | ENADC2 | ENADC1 | ENADC0  | W   |

| \$0018 | IENMI    | 00H  | -     | -    | -    | -    | -      | -      | INTE0  | INTMUTE | RW  |

| \$001B | IEIRQ2   | 00H  | -     | -    | -    | -    | -      | INTV   | INTE1  | INTMR   | RW  |

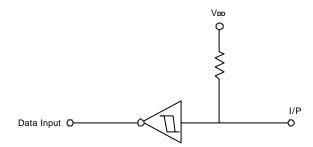

Figure 12.5. I/O Structure

#### 12.3. PORT2: P20 - P27

PORT2, an 8-bit bi-directional I/O port (Figure 12.5), may be programmed as an input or output pin by the software control. When setting the PT2DIR control bit to '0', its correspondent pin will act as an output pin. On the other hand, clear PT2DIR bit to '1', act as input pin. When programmed as an input, it has an internal pull-up resistor. When programmed as an output, the data to be output is latched to the port data register and output to the pin with push-pull structure. This port acts as input port after reset.

| Addr.  | Register | INIT | Bit7  | Bit6  | Bit5  | Bit4  | Bit3   | Bit2   | Bit1   | Bit0   | R/W |

|--------|----------|------|-------|-------|-------|-------|--------|--------|--------|--------|-----|

| \$0002 | PT2DIR   | FFH  | P270E | P260E | P25OE | P24OE | P23OE  | P22OE  | P210E  | P20OE  | W   |

| \$0003 | PT2      | FFH  | P27   | P26   | P25   | P24   | P23    | P22    | P21    | P20    | RW  |

| \$0010 | ENADC    | FFH  | CSTA  | -     | -     | -     | ENADC3 | ENADC2 | ENADC1 | ENADC0 | W   |

| \$0029 | CH1CON   | FFH  | ENDDC | MD1/2 | SRW   | START | STOP   | RXACK  | TXACK  | -      | RW  |

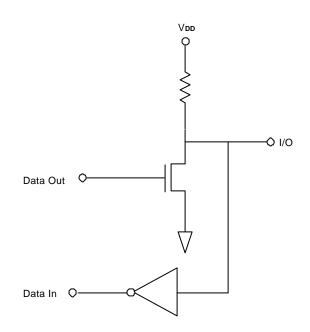

#### 12.4. PORT3: P30 - P31

PORT3 is an 2 bit bi-directional open-drain I/O port (Figure 12.6). Each pin of PORT3 may be bit programmed as an input or output port with open drain structure. When PORT3 works as output, the data to be output is latched to the port data register and output to the pin. When PORT3 pins that have '1's written to them, users must connect PORT3 with external pulled-up resistor and then PORT3 can be used as input (the input signal can be read). This port output HIGH after reset.

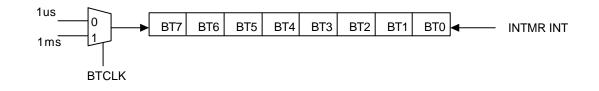

P30、P31 include Schmitt Trigger buffers for noise immunity and can be configured as the fC pins SDA0 & SCL0 respectively. If set  $\overline{\text{ENDDC}}$  to LOW in CH0DDC control register, P30、P31 will act as SDA0 & SCL0 I/O pins respectively and will be an open drain structure (Figure 12.6). After the chip is reset, this  $\overline{\text{ENDDC}}$  bit will be in HIGH state and PORT3 will act as I/O pins.

| Addr.  | Register | INIT | Bit7  | Bit6  | Bit5 | Bit4  | Bit3 | Bit2  | Bit1  | Bit0 | R/W |

|--------|----------|------|-------|-------|------|-------|------|-------|-------|------|-----|

| \$0004 | PT3      | FFH  | -     | -     | -    | -     | -    | -     | P31   | P30  | RW  |

| \$0029 | CH1CON   | FFH  | ENDDC | MD1/2 | SRW  | START | STOP | RXACK | TXACK | -    | RW  |

-0 I/O

Figure 12.6. PORT3

#### 12.5. PORT4: P40 - P41

PORT4 is available only on the 42pin SDIP IC. PORT40 - PORT41 is an 2-bit bi-directional CMOS I/O port with PMOS as internal pull-up (Figure 12.1). Each bi-directional I/O pin may be bit programmed as an input or output port without software control the data direction register. When PORT4 works as output, the data to be output is latched to the port data register and output to the pin. PORT4 pins that have '1's written to them are pulled HIGH by the internal PMOS pull-ups. In this state they can be used as input. The input signal can be read. This port outputs HIGH after reset.

| Addr.  | Register | INIT | Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 | R/W |

|--------|----------|------|------|------|------|------|------|------|------|------|-----|

| \$0005 | PT4      | FFH  | -    | -    | -    | -    | -    | -    | P41  | P40  | RW  |

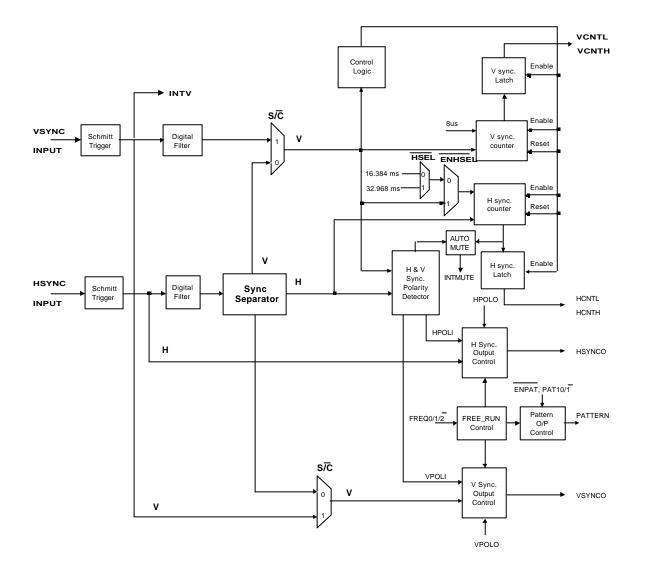

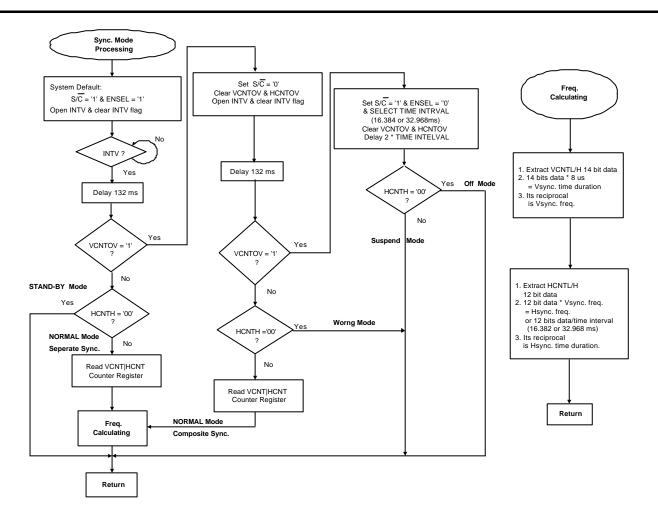

#### 13. H/V Sync Signals Processor

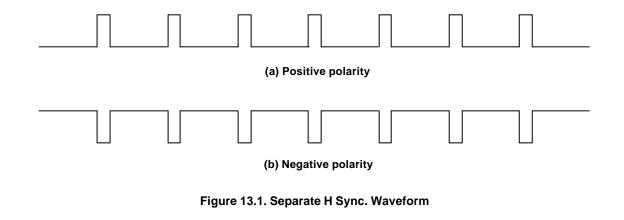

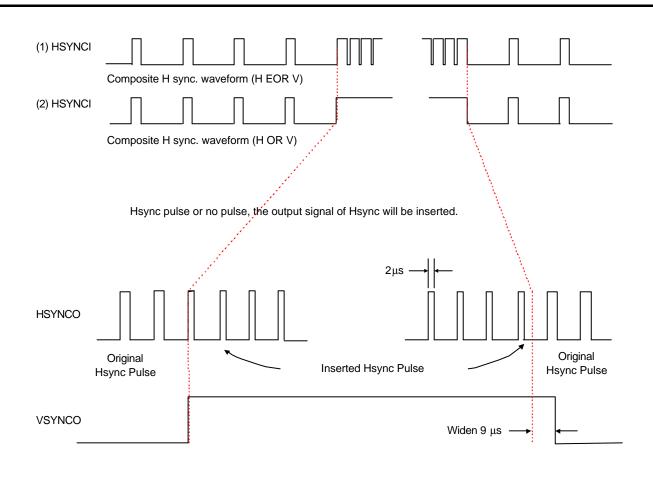

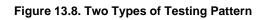

The functions of the sync processor include polarity detection, Hsync & Vsync signals counting, and programmable sync signals output. It also provides 3-sets of free running signals and special output of test pattern at burn-in process when activating the free running output function. The NT68P62 can properly handle either composite or separate sync signal inputs even without sync signal input. As to processing the composite sync signal, a hardware separator will be activated to extract the HSYNC signal under user controlled. The input at HSYNCI can be either a pure horizontal sync signal or a composite sync signal. For the sync waveform refer to Figure 13.1 & Figure 13.2.

The sync processor block diagram is shown in Figure 13.3. Both VSYNCI & HSYNCI pins have Schmitt Trigger and filtering process to improve noise immunity. Any pulse that is shorter than 125 ns, will be regarded as a glitch and will be ignored.

#

(a) Positive Polarity

(b) Negative Polarity

Figure 13.2. Composite H Sync. Waveform

Figure 13.3. Sync. Processor Block Diagram

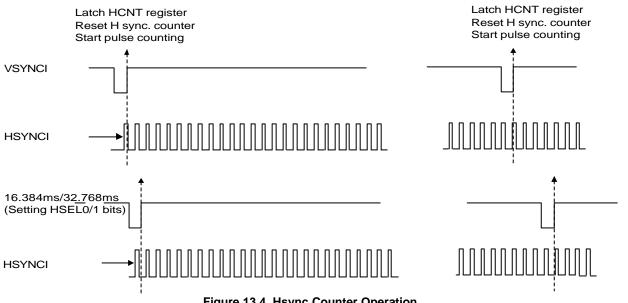

#### 13.1. V & H Counter Register: VCNTL/H, HCNTL/H

Vsync counter: VCNTL/H, the 14-bit READ ONLY register, contains information of the Vsync frequency. An internal counter counts the numbers of 8us pulse between two VSYNC pulses. When a next VSYNC signal is recognized, the counter is stopped and the VCNTH/L register latches the counter value and then the counter counts from zero again for evaluating next VSYNC time interval. The counted data can be converted to the time duration between two successive Vsync pulses by time 8 us. If no VSYNC incoming, the counter will overflow and set VCNTOV bit (in VCNTH register) to HIGH. Once the VCNTOV set to HIGH, it keeps in the HIGH state until writing '1' to it (CLRVOV bit).

Hsync counter: If the ENHSEL bit is set to HIGH, the internal counter counts the Hsync pulses between two Vsync pulses. The HCNTL/H control registers contain the numbers of Hsync pulse between two Vsync pulses. These data can determine if the Hsync frequency is valid or not to determine the accurate video mode.

The system supports two other options of interval for user counting the frequency of Hsync pulses. If users clear the ENHSEL and set the HSEL bits properly, this internal counter counts the Hsync pulses during this system defined time interval. The time interval is defined below:

| ENHSEL | HSEL | Hsync Freq | Note                                  |

|--------|------|------------|---------------------------------------|

| 1      | -    | Disabled   | After system reset or users disabling |

| 0      | 0    | 16.384 ms  |                                       |

| 0      | 1    | 32.768 ms  |                                       |

After system reset, this interval will be disabled and the content of ENHSEL & HSEL0 bits are '1'. When this function is disabled, the HCNTL/H counter is working on the VSYNC pulse. It is invalid to write '00' to them.

Latching the hsvnc counter: The counted value will be latched by the HCNTH/L register pairs which are updated by Vsync pulse or system defined time interval. (Refer the Figure 13.4 for the opration of HCNTL/H counter.) If the counter overflows, the HCNTOV bit (in HCNTH register) will be set to HIGH. Once the HCNTOV is set to HIGH, it keeps in the HIGH state until writing '1' to it (CLRHOV bit). When setting this CLRHOV bit, the HCNT counter will not be reset to zero.

Figure 13.4. Hsvnc Counter Operation

Figure 13.5. Composite H & V Sync. Processing

Figure 13.6. H & V Sync. Software Control Flow Chart (for reference only)

#### 13.2. Sync Processor Control Register:

Polarity: The detection of Hsync or Vsync polarity is achieved by hardware circuit that samples the sync signal's voltage level periodically. Users can read HPOLI & VPOLI bit from HVCON register, which bit = '1' represents positive polarity and '0' represents negative polarity. Furthermore, users can read HSYNCI and VSYNCI bit in HVCON register to detect H & V sync input signal. Users can control the polarity of H & V sync output signal by writing the appropriate data to the HPOLO and VPOLO bits in the HVCON register, '1' represents positive polarity and '0', negative polarity.

Composite sync: Users have to determine whether the incoming signal is separate sync or composite sync and set

S/C & ENHSEL/HSEL bit properly. If the input sync

signal is composite, after set  $S/\overline{C}$  to '0', the sync separator block will be activated (please refer Figure 13.5). At the area of Vsync pulse, there can exist Hsync pulses or not. For the output of Hsync, users can active hardware to interpolate the Hsync pulses in that area by clearing the

INSEN bit. The width of these inserted pulses is 2uS fixed and the time interval is the same as previous one. According to the last Hsync pulse outside the Vsync pulse duration, the hardware will arrange the interval of these hardware interpolated pulses. These inserted Hsync pulse have 125 nS phase deviation maximum. The Vsync pulse can be extracted by hardware from composite Hsync signal, and the delay time of output Vsync signal will be limited bellow 20ns. For inserting Hsync pulse safely, the extracted Vsync pulse will be widens about 9µs. Because evenly inserting the Hsync pulse, the last inserted Hsync pulse will have different frequency from original ones.

System will not implement this insertion function, users

| must clear INSEN bit in the SYNCON control register to                                                                                  |

|-----------------------------------------------------------------------------------------------------------------------------------------|

| activate this function. After reset, $S/\overline{C}$ & $\overline{INSEN}$ bits default value is HIGH and clear the VCNT   HCNT counter |

| latches to zero.                                                                                                                        |

Sync output: In pin assignment, VSYNCO & HSYNCO represent Vsync & Hsync output which are shared with P06