**SAA9056**

### **GENERAL DESCRIPTION**

The SAA9056 is designed to provide colour difference signals for a digital TV signal processing system.

#### **Features**

- Phase-linear chrominance bandpass filter for cross-colour improvement

- Programmable filter characteristics for optimum adaption for different IF stages

- Recursive "Cloche" (Bell) filter

- Zero-crossing detection, FM demodulator with high AM rejection

- · One demodulator for both carrier frequencies

- Base-band signal adjustment in gain and offset

- De-emphasis with recursive filter structure

- Line delay and cross-over switch for colour difference signals

- Output multiplexer for the UV format of the Digital Multistandard Secam Decoder

- Standard identification circuit with programmable sensitivity

- Programmable I<sup>2</sup>C-bus address

### PACKAGE OUTLINE

28-lead DIL; plastic (SOT117).

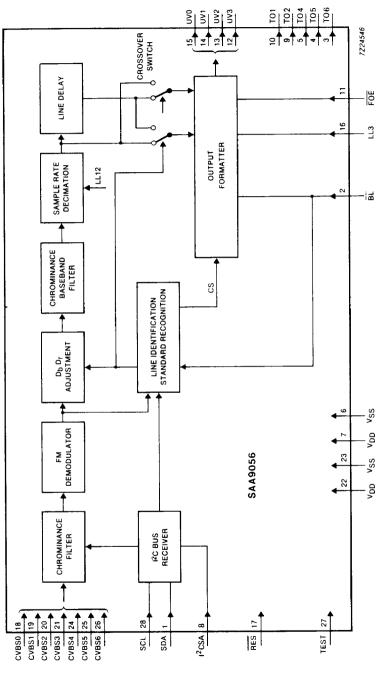

Fig. 1 Block diagram.

August 1989

3-289

**SAA9056**

| PINNING              |                    |          |                    |                                                                                 |

|----------------------|--------------------|----------|--------------------|---------------------------------------------------------------------------------|

|                      |                    | 1        | SDA                | I <sup>2</sup> C-bus serial data input, receive only, no                        |

|                      |                    |          |                    | data is transmitted from the SDSD                                               |

|                      |                    | 2        | BL                 | This signal from the digital multistandard                                      |

|                      |                    |          |                    | decoder indicates the active video and                                          |

|                      |                    | •        | <b>TO</b> 0        | line blanking period                                                            |

|                      |                    | 3        | T06                | Test output pin, used during test mode                                          |

|                      |                    | 4        | TO5                | only. Do not connect this pin                                                   |

|                      |                    | 5        | TO4                | As pin 3<br>As pin 3                                                            |

|                      |                    | 6        | V <sub>SS</sub>    | Ground                                                                          |

|                      | <del></del>        | 7        | V <sub>DD</sub>    | + 5 V supply                                                                    |

| SDA 1                | 28 SCL             | 8        | I <sup>2</sup> CSA | 1 <sup>2</sup> C-bus select address. Input to select two                        |

|                      |                    |          |                    | different 12C-bus slave addresses                                               |

| BL 2                 | 27 TEST            | 9        | TO2                | As pin 3                                                                        |

| то6 3                | 26 CVBS6<br>(MSB)  | 10       | TO1                | As pin 3                                                                        |

| TO5 4                | 25 CVBS5           | 11       | FOE                | Fast output enable signal, forces the                                           |

| $\exists$            |                    |          |                    | UV-outputs to High-Z state                                                      |

| TO4 5                | 24 CVBS4           | 12       | UV3                | UV colour difference signals, via this port                                     |

| V <sub>SS</sub> 6    | 23 V <sub>SS</sub> |          |                    | the decoded colour difference signals are                                       |

|                      |                    |          |                    | transmitted to the DMSD in a mixed                                              |

| VDD 7                | 22 V <sub>DD</sub> |          |                    | parallel/serial format. Additionally the                                        |

| I <sup>2</sup> CSA 8 | 21 CVBS3           |          |                    | status flag CS (colour in SECAM detected) is encoded in the UV data stream. The |

| то2 9                | 20 CVBS2           |          |                    | output drivers can be set to high impedance                                     |

| 102 💆                | 20] CVB32          |          |                    | (3-state) via the I <sup>2</sup> C-bus.                                         |

| TO1 10               | 19 CVBS1           | 13       | UV2                | As pin 12                                                                       |

| FOE 11               | 18 (LSB)           | 14       | UV1                | As pin 12                                                                       |

| $\exists$            | (238)              | 15       | UV0                | As pin 12                                                                       |

| UV3 12               | 17 RES             | 16       | LL3                | LL3 is the line-locked system clock at                                          |

| UV2 13               | 16 LL3             |          |                    | 13.5 MHz                                                                        |

| UV1 14.              | 15 UV0             | 17       | RES                | The reset signal (active LOW) disables the                                      |

| 001 [14]             | 15 000             |          |                    | UV buffers, Minimum LOW-time on this                                            |

|                      | 7Z24548            | 18       | CVBS0              | input = 10 LL3-cycles<br>Composite video, blanking and synchro-                 |

|                      |                    | ,,,      | 01200              | nization (LSB) input                                                            |

| Fig.2 Pinn           | ing diagram.       | 19       | CVBS1              | As pin 18                                                                       |

|                      |                    | 20       | CVBS2              | As pin 18                                                                       |

|                      |                    | 21       | CVBS3              | As pin 18                                                                       |

|                      |                    | 22       | $v_{DD}$           | As pin 7                                                                        |

|                      |                    | 23       | $V_{SS}$           | As pin 6                                                                        |

|                      |                    | 24       | CVBS4              | Composite video, blanking and synchro-                                          |

|                      |                    |          | 0) (0.05           | nization                                                                        |

|                      |                    | 25<br>26 | CVBS5              | As pin 24                                                                       |

|                      |                    | 26<br>27 | CVBS6<br>TEST      | As pin 24 (MSB) This signal (active HIGH) enables the                           |

|                      |                    | 21       | 1631               | scan test mode                                                                  |

|                      |                    | 28       | SCL                | 1 <sup>2</sup> C-bus serial clock input                                         |

|                      |                    | _        | •                  |                                                                                 |

**SAA9056**

#### **FUNCTIONAL DESCRIPTION**

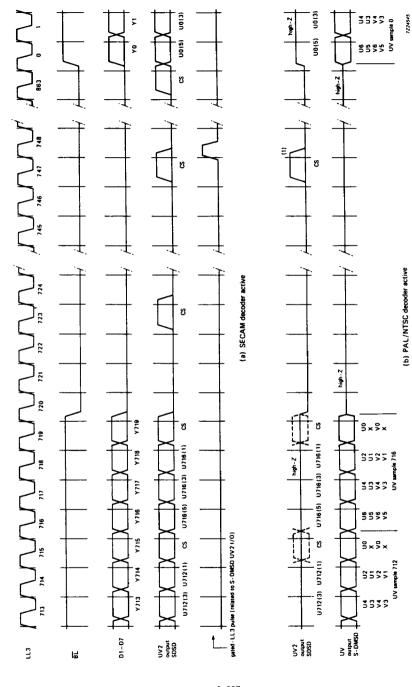

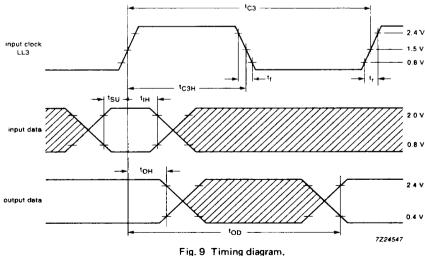

The S-VHS Digital SECAM Decoder (SDSD) forms an integral part of a digital TV signal processing system. The system incorporates a Video Processor and Input Selector (TDA9045), an A/D Converter (SAA9079), a Sample Rate Converter (SAA9058), a Digital Multi-Standard Decoder with separate chrominance and luminance input (SAA9051), a Digital Deflection Controller (SAA9062/3/4)\*, a Clock Generator Circuit (SAA9057), a Video Processor with DACs (SAA9060), a Colour Transient Improvement Circuit (TDA4565), a Video Control Combination Circuit (TDA4580), and an Octuple 6-bit DAC and a Feature Box. Figure 9 illustrates the timing of the input and output signals relative to the input clock (LL3).

The S-DMSD (SAA9051) decodes and demodulates the colour information from all TV standards which employ a quadrature modulated colour carrier. The S-DMSD also processes the luminance and synchronization signals and generates auxiliary signals.

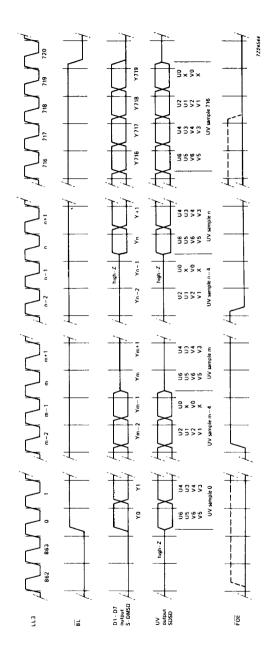

The SDSD separates the colour information which it demodulates and decodes to provide the colour difference signals. These signals are subsequently encoded to produce a serial/parallel data stream at the UV outputs. Figure 4 illustrates the formatting and timing of the UV output port.

To enable other sources (eg PIP-CO) to access the digital YUV-bus, a fast output enable signal (FOE) is provided. Two LL3-cycles after the FOE becomes inactive (HIGH), the UV output port of the SDSD is forced to the High-Z state. When the FOE signal is active (LOW) again, it needs two LL3-cycles and the UV output port of the SDSD becomes active (see Fig.4).

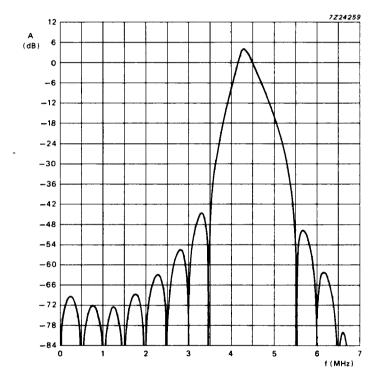

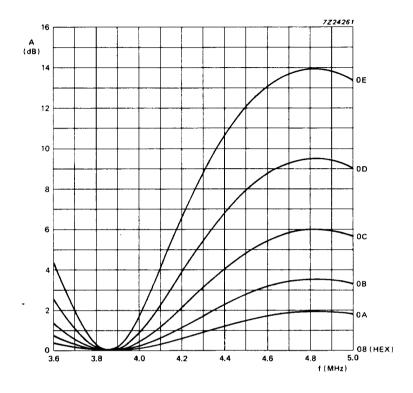

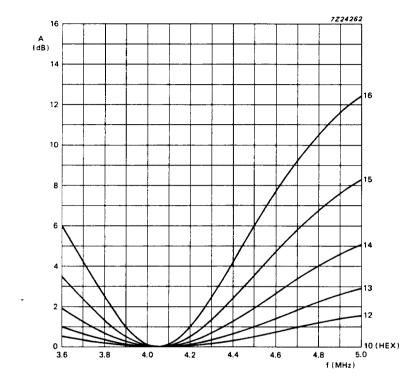

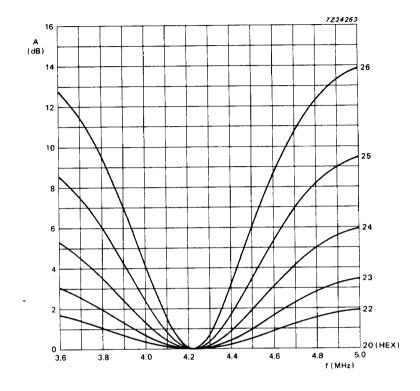

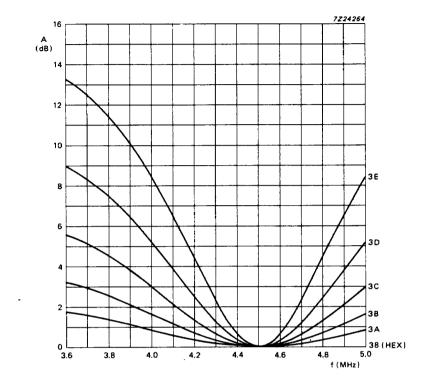

The chrominance bandpass filter for separating the frequency modulated colour carrier consists of several phase-linear FIR filters which improve the cross-colour behaviour. The non-linear phase (Bell) filter has a recursive structure (IIR filter). Figure 3 illustrates the frequency response of the chrominance band-pass filter and Bell filter. One of the FIR filters can be programmed via the I<sup>2</sup> C-bus to provide optimal adaption for the various IF stages. Different responses can be selected by means of a 7-bit control word. Figure 8 illustrates some examples of frequency responses of the programmable adaptive filer.

Only one FM demodulator is used to demodulate the chrominance signal; this accomodates both carrier frequencies regardless of the centre frequency. It is a zero-crossing demodulator with a real time divider which is a pipeline structure. After demodulation the baseband signal is adjusted, line sequentially, to the appropriate colour difference signal. During the clamping period, the demodulated reference carrier is compared with the previous reference signal by the line identification circuit. The identification circuit compares the phase of the two demodulated burst signals and, if the phase relationship is incorrect for several lines (not SECAM), the CS flag (colour in SECAM) will be reset.

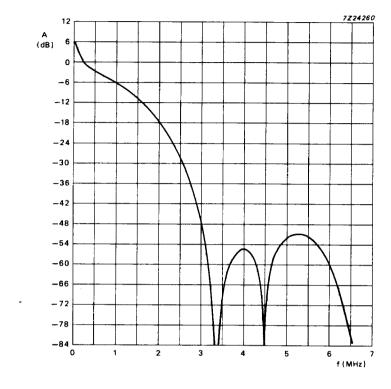

The baseband filter consists of a linear phase low-pass filter together with a de-emphasis filter with a recursive structure. Figure 5 illustartes the frequency response of the de-emphasis and band-pass filters for the colour difference signals. After filtering, the sample rate is reduced to a quarter (LL12 = 3.375 MHz). The word length is truncated to seven bits. The resultant signal is delayed by one line period (64  $\mu$ s = 216 clock periods of 3.375 MHz). The signals, delayed and non-delayed, can be switched either directly or cross-wise to two different outputs which correspond to the colour difference signals.

The cross-over switch is controlled by the line identification circuit. At the end of the chrominance path an output formatter transforms the 14 bits ( $2 \times 7$  bits clocked by 3.375 MHz) to a 4-bit wide channel which is clocked by 13.5 MHz (LL3). The bits are separated into odd and even and then serialized.

\* The digital TV signal processing system has the option of using one of three Digital Deflection Controllers (SAA9062/3/4). The choice of DDC is dependent on the format of the CRT and the line/field frequency.

**SAA9056**

The format for the UV output is the same as that of the UV I/O port in the S-DMSD (SAA9051). The timing multiplexer is controlled by the external signal  $\overline{BL}$  from the S-DMSD. Signal  $\overline{BL}$  is also used as a line-locked synchronization signal to generate several internal burst gate pulses.

The CS flag is transmitted via the chrominance data-stream because the SDSD has no I<sup>2</sup>C-bus transmitter. The CS bit is read once per line by the S-DMSD at LL3 clock cycle number 748 (see Fig.6). If no SECAM colour is detected the UV port will be set to zero. After reset the UV lines will be set to high impedance (3-state) and the SDSD must be re-initialized via the I<sup>2</sup>C-bus to enable further operation.

Fig. 3 Frequency response of chrominance bandpass and Bell filter.

Fig.4 Timing of FOE signal.

Fig. 5 Frequency response of the de-emphasis and base-band filter for the colour difference signals.

Fig.6 Position of CS signal read by S-DMSD.

(1) The CS signal is active only for  $\pm\,64$  clock pulses (LL3) around the gate pulse.

August 1989

3-295

**SAA9056**

#### I<sup>2</sup>C-BUS PROTOCOL

#### Slave receiver organization

Two different slave addresses are programmable with the I2CSA input at pin 8

| I <sup>2</sup> CSA | slave | slave receiver addresses |    |    |    |    |    |                    |  |  |  |  |

|--------------------|-------|--------------------------|----|----|----|----|----|--------------------|--|--|--|--|

|                    | A6    | A5                       | Α4 | А3 | A2 | Α1 | Α0 | *)                 |  |  |  |  |

| 0 or unconnected   | 1     | 0                        | 0  | 0  | 1  | 0  | 1  | 0 (bin) = 8A (hex) |  |  |  |  |

| 1                  | 1     | 0                        | 0  | 0  | 1  | 1  | 1  | 0 (bin) = 8E (hex) |  |  |  |  |

<sup>\*) 0 =</sup> receiver mode

Fig. 7 Slave receiver format.

Table 1 Subaddress definition

| register<br>function             | subaddress<br>(HEX) | D7<br>(MSB) | D6  | D5  | D4  | D3  | D2  | D1  | DO<br>(LSB) |

|----------------------------------|---------------------|-------------|-----|-----|-----|-----|-----|-----|-------------|

| Main counter start address       | 10                  | MA1         | MAO | Х   | DT4 | DT3 | DT2 | DT1 | DTO         |

| (MA9MA0)                         | 11                  | MA9         | MA8 | MA7 | MA6 | MA5 | MA4 | МАЗ | MA2         |

| Burst gate begin                 | 12                  | ВВ7         | вв6 | BB5 | BB4 | ввз | BB2 | BB1 | вво         |

| Burst gate end                   | 13                  | BE7         | BE6 | BE5 | BE4 | BE3 | BE2 | BE1 | BEO         |

| Standard recognition sensitivity | 14                  | R7          | R6  | R5  | R4  | R3  | R2  | R1  | R0          |

| Programmable adaptive filter     | 15                  | ×           | P6  | P5  | P4  | Р3  | P2  | P1  | PO          |

| Control register                 | 16                  | ×           | x   | ×   | X   | ×   | C2  | C1  | CO          |

| Reserved                         | 17-1F               | ×           | ×   | ×   | ×   | ×   | x   | ×   | x           |

### Notes to Table 1

- The subaddress is automatically incremented to enable quick initialization by the I<sup>2</sup>C-bus controller within one transmission.

- 2. All eight bits of the subaddress are decoded by the device.

- 3. The subaddresses shown are acknowledged by the device. Subaddresses 00 to 0F (reserved for the Digital Multi-Standard Decoder) are not acknowledged. The subaddress counter wraps-around from 1F to 00. Subaddresses 20 to FF are not allowed.

- 4. X = don't care.

- 5. After power-on-reset the control register (subaddress 16) is set to logic 0, all other registers are undefined.

### Subaddress 10 and 11 (HEX)

Main counter start address.

Application dependent.

| ма9         | ма8 | MA7 | ма6 | MA5 | MA4 | MA3 | MA2 | MA1 | MAO |                 | delay time                                                  |

|-------------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----------------|-------------------------------------------------------------|

| 0<br>-<br>- | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 1   | + 511<br>-<br>- | outside central<br>counter range                            |

| _<br>_<br>0 | 1   | 1   | 0   | 1   | 0   | 0   | 0   | 1   | 0   | -<br>-<br>+ 418 | •                                                           |

| 0<br>-<br>- | 1   | 1   | 0   | 1   | 0   | 0   | 0   | 0   | 1   | + 417<br>-<br>- | 417 x 74 ns $\approx$ + 31 $\mu$ s (maximum positive value) |

| -<br>0<br>0 | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 1   | -<br>+ 1<br>0   | + 74 ns<br>reference point*                                 |

<sup>\*</sup> Reference point position to be fixed.

| MA9 | MA8 | ма7 | MA6 | MA5 | MA4 | MA3 | MA2 | MA1 | мао |                   | delay time                                                       |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-------------------|------------------------------------------------------------------|

| 1   | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 1   | -1                | -74 ns                                                           |

| _   |     |     |     |     |     | ,   |     |     | ]   | -                 |                                                                  |

| _   |     |     |     |     |     |     |     |     |     | _                 |                                                                  |

| _   |     |     |     |     |     |     |     |     |     | _                 |                                                                  |

| 1   | o   | 0   | 1   | 0   | 0   | 0   | 0   | 1   | 0   | -446              | $-446 \times 74$ ns $\approx -33 \mu$ s (maximum negative value) |

| 1   | 0   | 0   | 1   | 0   | 0   | 0   | 0   | 0   | 1   | -447 <sub>1</sub> |                                                                  |

| _   |     |     |     |     |     |     |     | ļ   |     | -                 |                                                                  |

| _   |     | ļ   |     |     |     |     |     |     |     | _                 | outside central                                                  |

| _   |     |     |     |     |     |     |     |     |     |                   | counter range                                                    |

|     |     |     |     |     |     |     |     |     |     | _                 |                                                                  |

| 1   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | _512 <sup>′</sup> |                                                                  |

Stepsize =

$$\frac{1}{13.5 \text{ MHz}}$$

= 74 ns

Internal counter range: -446 to +417

**SAA9056**

#### Subaddress 12 (HEX)

Burst gate begin (start time)

Application dependent.

| ВВ7 | BB6 | BB5 | ВВ4 | ввз | BB2 | BB1 | BB0 | dec | delay time           |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|----------------------|

| 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | zero reference point |

| 0   | 0   | 0   | 0   | 0   | 0   | 0   | 1   | 1   | 74 ns                |

| -   | -   | -   | _   | -   | _   | _   | _   | _   |                      |

| -   | —   | - ' | _   | -   | _   | _   | _   | _   |                      |

| 1   | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 255 | 18.89 μs             |

Stepsize =

$$\frac{1}{13.5 \text{ MHz}}$$

= 74 ns

#### Subaddress 13 (HEX)

Burst gate end (stop time)

Application dependent.

| BE7 | BE6 | BE5 | BE4 | BE3 | BE2 | BE1 | BEO | dec | delay time           |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|----------------------|

| 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | zero reference point |

| 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 1   | 74 ns                |

| -   | -   | _   | -   | -   | _   | -   | -   | _   | _                    |

| -   | -   | _   | _   | -   | _   | _   | ' — | -   | _                    |

| 1   | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 255 | 18.89 μs             |

Stepsize =

$$\frac{1}{13.5 \text{ MHz}}$$

= 74 ns

The stop time must be greater than the start time.

The reference point position of the burst gate start/stop time is identical with the main counter zero position.

**SAA9056**

## Subaddress 14 (HEX)

Standard recognition sensitivity

Application dependent

| R7 | R6 | R5 | R4 | R3 | R2 | R1 | RO | function                                                                                                                              |

|----|----|----|----|----|----|----|----|---------------------------------------------------------------------------------------------------------------------------------------|

|    | 0  | 0  | 0  | 0  | 0  | 0  | 0  | relationship between the number of line identification errors related to a window of 312 lines  0:312 theoretical highest sensitivity |

| 0  | 0  | 0  | U  | U  | U  | 10 | "  |                                                                                                                                       |

| 0  | 0  | 0  | 0  | 0  | 0  | 0  | 1  | 1 : 312                                                                                                                               |

| 0  | 0  | 0  | 1  | 1  | 0  | 0  | 1  | 25 : 312                                                                                                                              |

| 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 255 : 312 theoretical lowest sensitivity                                                                                              |

For programmed numbers from 0 to approximately 25 (dec) the colour signal is switched off. With the value 25 (dec) the colour signal will be enabled only when extremely good signal quality is present. If the colour signal quality is reduced, i.e. VCR signal source, bad S/N ratio, bad quantization, diminished colour carrier and insufficient IF adaption, the sensitivity should be set lower (higher programmed number up to 255 (dec) in order to prevent excessive switching and thus ensure constant colour.

SAA9056

#### Subaddress 15 (HEX)

Programmable adaptive filter PAF (P6-P0)

Application (IF stage) dependent

The programmable adaptive filter, together with the cloche and linear bandpass filter, forms a filter-curve that treats the chrominance frequency spectra with different gain but linear phase. The frequency characteristic is a system of sinusoidal waveforms which are described by:

- Reference "knots" of constant gain (0 dB)

- Frequency points ("tops") with maximum gain

- The amount of maximum gain

(There is also a switchable pre-amplifier in another stage of the bandpass filter).

The components of the PAF can be programmed via the  $1^2$ C-bus by using device address 8A (or 8E) and subaddress 15 thereby producing 57 different transfer functions. An example of some transfer functions is given in Figure 8 (a) to (d).

| MSB | P6                    | P5                    | P4                    | Р3                    | P2                         | P1                         | PO                              | function                                              |                |                |                         |

|-----|-----------------------|-----------------------|-----------------------|-----------------------|----------------------------|----------------------------|---------------------------------|-------------------------------------------------------|----------------|----------------|-------------------------|

|     | X<br>X<br>X<br>X<br>X | X<br>X<br>X<br>X<br>X | X<br>X<br>X<br>X<br>X | X<br>X<br>X<br>X<br>X | 1<br>1<br>1<br>0<br>0<br>0 | 1<br>0<br>0<br>1<br>1<br>0 | 1<br>0<br>1<br>0<br>1<br>0<br>1 | maximum 19 dB 14 dB 9.5 dB 6 dB 3.5 dB 2 dB 1 dB 0 dB | n gain at tops |                |                         |

|     |                       |                       |                       |                       |                            |                            |                                 | position o                                            | of tops and k  | nots (MHz)     |                         |

|     |                       |                       |                       | ,                     |                            |                            |                                 | top                                                   | knot           | top            | Figs 8a—d               |

|     | X<br>X                | 1                     | 1<br>1                | 1<br>0                | X<br>X                     | X<br>X                     | X<br>X                          | 3.375<br>4.5                                          | 4.5<br>5.625   | 5.625<br>6.75  | + A/dB (d)<br>-A/dB (d) |

| _   | ×                     | 1                     | 0<br>0                | 1<br>0                | X<br>X                     | X<br>X                     | X<br>X                          | 4.219<br>3.375                                        | 5.063<br>4.219 | 5.906<br>5.063 | -A/dB (c)<br>+ A/dB (c) |

| _   | X<br>X                | 0                     | 1<br>1                | 1<br>0                | X<br>X                     | X<br>X                     | X<br>X                          | 4.05<br>2.7                                           | 5.4<br>4.05    | 6.75<br>5.4    | -A/dB (b)<br>+ A/dB (b) |

| _   | X<br>X                | 0                     | 0<br>0                | 1<br>0                | ×                          | X<br>X                     | X<br>X                          | 2.89<br>3.86                                          | 3.86<br>4.82   | 4.82<br>5.79   | + A/dB (a)<br>A/dB (a)  |

| _   | 1<br>0                | ×                     | X<br>X                | X<br>X                | ×                          | ×                          | ×                               | additiona<br>times two<br>times one                   |                | cation         |                         |

| *   | Х                     | X                     | Х                     | ×                     | X                          | X                          | X                               | * MSB no                                              | ot used        |                |                         |

Fig. 8(a) Examples of frequency response for the programmable adaptive filter; from 08 to 0E (HEX).

Fig. 8(b) Example of frequency response for the programmable adaptive filter; from 10 to 16 (HEX).

Fig. 8(c) Example of frequency response for the programmable adaptive filter; from 20 to 26 (HEX).

Fig. 8(d) Example of frequency response for the programmable adaptive filter; from 38 to 3E (HEX).

**SAA9056**

### Subaddress 16 (HEX)

DSD control 3 register

| C2 | C1 | СО | UV-output                                                                                                             |

|----|----|----|-----------------------------------------------------------------------------------------------------------------------|

| ×  | 0  | 1  | active zero whole line                                                                                                |

| ×  | 1  | 0  | colour enable (if CS flag then colour on)                                                                             |

| х  | 1  | 1  | colour forced on (independent of CS flag)                                                                             |

| 0  | х  | ×  | positive UV                                                                                                           |

| 1  | х  | ×  | negative UV                                                                                                           |

| 0  | 0  | 0  | 3-state                                                                                                               |

| 1  | 0  | 0  | UV2-output active during horizontal blanking period (CS-bit* transmission); high impedance in active line negative UV |

After power-on reset the control register is set to logic 0.

\* The position of the CS transmission is dependent on the start value of the main counter (Reg 10 and 11).

Purchase of Philips' I<sup>2</sup>C components conveys a license under the Philips' I<sup>2</sup>C patent to use the components in the I<sup>2</sup>C-system provided the system conforms to the I<sup>2</sup>C specifications defined by Philips.

**SAA9056**

### RATINGS

Limiting values in accordance with the Absolute Maximum System (IEC 134)

| parameter                           | conditions               | symbol           | min. | max. | unit |

|-------------------------------------|--------------------------|------------------|------|------|------|

| Supply voltage                      |                          | V <sub>DD</sub>  | -0.5 | 7.0  | ٧    |

| Voltage input                       |                          | VI               | -0.5 | 7.0  | V    |

| Voltage output                      | I <sub>max</sub> = 20 mA | Vo               | -0.5 | 7.0  | V    |

| Total power dissipation             |                          | P <sub>tot</sub> | _    | 1.2  | w    |

| Operating ambient temperature range |                          | Tamb             | 0    | 70   | oC.  |

| Storage temperature range           |                          | T <sub>stg</sub> | -65  | 150  | oC.  |

#### **HANDLING**

Inputs and outputs are protected against electrostatic discharge in normal handling. However, to be totally safe, it is good practice to take normal precautions appropriate to handling MOS devices (see 'Handling MOS devices').

**SAA9056**

### **CHARACTERISTICS**

$V_{DD}$  = 4.5 to 5.5 V;  $T_{amb}$  = 0 to 70 °C; unless otherwise specified. All voltages are referenced to ground (pins 6 and 23) unless otherwise specified.

| parameter                                                            | conditions                | symbol           | min. | typ.     | max.            | uni |

|----------------------------------------------------------------------|---------------------------|------------------|------|----------|-----------------|-----|

| Supply voltage                                                       |                           | $V_{DD}$         | 4.5  | _        | 5.5             | ٧   |

| Supply current (f <sub>nom</sub> )                                   | V <sub>DD</sub> = 5.5 V   |                  |      |          |                 |     |

| Inputs LOW; outputs with maximum load                                |                           | <sup>1</sup> DD  | _    | _        | 180             | mA  |

| Inputs                                                               |                           |                  |      |          |                 |     |

| Input voltage LOW (clock data)<br>pins 2, 16, 17 to 21; and 24 to 27 |                           | VIL              | 0    | _        | 0.8             | v   |

| Input voltage LOW (I <sup>2</sup> C)<br>pins 1 and 28                |                           | VIL              | 0    | -        | 1.5             | v   |

| Input voltage HIGH (data)<br>pins 2, 17 to 21; and 24 to 27          |                           | ViH              | 2    | <u> </u> | V <sub>DD</sub> | v   |

| Input voltage HIGH (LL3)<br>pin 16                                   |                           | ViH              | 2.4  | -        | V <sub>DD</sub> | v   |

| Input voltage HIGH (I <sup>2</sup> C)<br>pins 1 and 28               |                           | VIH              | 3    | -        | VDD             | v   |

| Input leakage current<br>pins 1, 2, 12 to 21; and 24 to 27           |                           | l <sub>L</sub> i | -10  | _        | + 10            | μΑ  |

| Input current pins 8 and 11                                          |                           | կ                | -10  | -        | + 60            | μΑ  |

| Input capacitance (data)<br>pins 2, 18 to 21; and 24 to 27           |                           | CI               | 2    | -        | 7.5             | pF  |

| Input capacitance (clock)<br>pin 16                                  |                           | CI               | 5    | _        | 10              | pF  |

| Input capacitance (reset)<br>pin 17                                  |                           | Cį               | 2    | _        | 10              | pF  |

| Outputs                                                              |                           |                  |      |          |                 |     |

| Output voltage LOW<br>pins 3 to 5; 8 to 15                           | IOL = 2 mA                | VOL              | 0    | _        | 0.4             | v   |

| Output voltage LOW<br>SDA pin 1                                      | 10L = 5 mA                | VoL              | 0    | _        | 0.45            | v   |

| Output voltage HIGH pins 3 to 5; 8 to 15                             | I <sub>OL</sub> = -0.5 mA | Voн              | 2.4  | -        | VDD             | V   |

| Capacitive load of outputs in high impedance pins 12 to 15           |                           | Cz               | 2    |          | 15              | ρF  |

#### CHARACTERISTICS

$V_{DD}$  = 4.5 to 5.5 V;  $T_{amb}$  = 0 to 70 °C; unless otherwise specified. All voltages are referenced to ground (pins 6 and 23) unless otherwise specified.

| parameter             | conditions                  | symbol          | min. | typ. | max. | unit |

|-----------------------|-----------------------------|-----------------|------|------|------|------|

| Clock timing (LL3)    |                             |                 |      |      |      |      |

| Cycle time            | note 1                      | t <sub>C3</sub> | 69   | _    | 80   | ns   |

| Duty factor           |                             | δ               | 43   | _    | 57   | %    |

| Rise time             | note 2                      | t <sub>r</sub>  | -    | _    | 6    | ns   |

| Fall time             | note 2                      | t <sub>f</sub>  | -    | _    | 6    | ns   |

| Input timing          |                             |                 |      |      |      |      |

| Data set up time      |                             | tSU             | 12   | _    | _    | ns   |

| Data hold time        | note 3                      | tiH             | 5    | _    | _    | ns   |

| Output timing         |                             |                 |      |      |      |      |

| Data load capacitance |                             | CL              | 7.5  | _    | 50   | рF   |

| Data hold time        | V <sub>1H</sub> (CLK) = 3 V | <sup>t</sup> OH | 5    | _    |      | ns   |

| Data delay time       | C <sub>L</sub> = 25 pF      | tOD             | -    | _    | 45   | ns   |

#### Notes to the characteristics

- 1. Static deviation = ±2%; dynamic deviation = ±7% for signal path CVBS-DCVBS (this is required for the running-in of the DMSD sync processor).

- 2. The rising and falling edges of the clock signal are assumed to be smooth due to roll-off low-pass

- 3. Matches to SAA9058 for  $V_{1H}(LL3) \ge 3 \text{ V}$ .

August 1989

3-308