CMOS 8-Bit Microcontroller

#### TMP87PS71AF

The TMP87PS71A is a One-Time PROM microcontroller with low-power 480 K bits (60 Kbytes) electrically programmable read only memory for the TMP87CS71B system evaluation. The TMP87PS71A is pin compatible with the TMP87CS71B. The operations possible with the TMP87CS71B can be performed by writing programs to PROM. The TMP87PS71A can write and verify in the same way as the TC571000D using an adaptor socket BM11107 and an EPROM programmer.

| Product No. | OTP           | RAM            | Package            | Adapter Socket |

|-------------|---------------|----------------|--------------------|----------------|

| TMP87PS71AF | 60 K × 8 bits | 2.0 K × 8 bits | P-QFP80-1420-0.80B | BM11107        |

For a discussion of how the reliability of microcontrollers can be predicted, please refer to Section 1.3 of the chapter entitled Quality and Reliability Assurance / Handling Precautions.

TOSHIBA is continually working to improve the quality and reliability of its products. Nevertheless, semiconductor devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical stress. It is the responsibility of the buyer, when utilizing TOSHIBA products, to comply with the standards of safety in making a safe design for the entire system, and to avoid situations in which a malfunction or failure of such TOSHIBA

making a safe design for the entire system, and to avoid situations in which a malfunction or failure of such TOSHIBA products could cause loss of human life, bodily injury or damage to property.

In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in the most recent TOSHIBA products specifications. Also, please keep in mind the precautions and conditions set forth in the "Handling Guide for Semiconductor Devices," or "TOSHIBA Semiconductor Reliability Handbook" etc..

■ The TOSHIBA products listed in this document are intended for usage in general electronics applications (computer, personal equipment, office equipment, measuring equipment, industrial robotics, domestic appliances, etc.). These TOSHIBA products are neither intended nor warranted for usage in equipment that requires extraordinarily high quality and/or reliability or a malfunction or failure of which may cause loss of human life or bodily injury ("Unintended Usage"). Unintended Usage include atomic energy control instruments, airplane or spaceship instruments traffic signal instruments control instruments medical instruments. all types of transportation instruments, traffic signal instruments, combustion control instruments, medical instruments, all types of safety devices, etc.. Unintended Usage of TOSHIBA products listed in this document shall be made at the customer's

The products described in this document are subject to the foreign exchange and foreign trade laws.

The information contained herein is presented only as a guide for the applications of our products. No responsibility is assumed by TOSHIBA CORPORATION for any infringements of intellectual property or other rights of the third parties which may result from its use. No license is granted by implication or otherwise under any intellectual property or other rights of TOSHIBA CORPORATION or others.

The information contained herein is subject to change without notice.

3-71A-1 2002-07-02

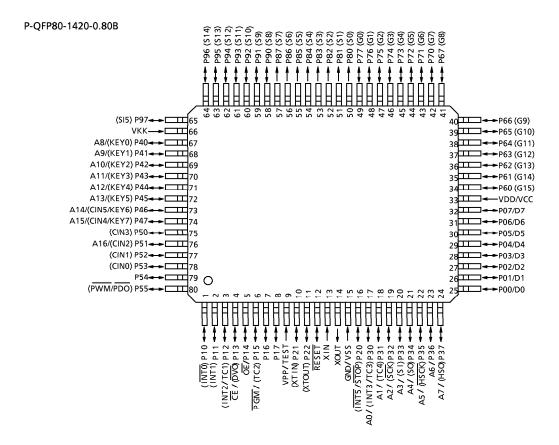

## Pin Assignments (Top View)

## **Pin Functions**

The TMP87PS71A has two modes: MCU and PROM.

(1) MCU mode

In this mode, the TMP87PS71A is pin compatible with the TMP87CS71B (fix the TEST pin at low level).

# (2) PROM mode

| Pin Name<br>(PROM mode) | Input/Output     | Functions                                              | Pin Name<br>(MCU mode) |

|-------------------------|------------------|--------------------------------------------------------|------------------------|

| A16                     |                  |                                                        | P51                    |

| A15 to A8               | Input            | PROM address inputs                                    | P47 to P40             |

| A7 to A0                |                  |                                                        | P37 to P30             |

| D7 to D0                | 1/0              | PROM data input/outputs                                | P07 to P00             |

| CE                      |                  | Chip enable signal input (active low)                  | P13                    |

| ŌĒ                      | Input            | Output enable signal input (active low)                | P14                    |

| PGM                     |                  | Program control input (active low)                     | P15                    |

| VPP                     |                  | + 12.75 V/5 V (Program supply voltage)                 | TEST                   |

| vcc                     | Power supply     | + 6.25 V/5 V                                           | VDD                    |

| GND                     |                  | ov                                                     | vss                    |

| P55 to P52              |                  | Pull-down with resistance for input processing         |                        |

| P11                     |                  |                                                        |                        |

| P21                     |                  | PROM mode setting pin. Be fixed at high level.         |                        |

| P50                     |                  |                                                        |                        |

| P17, P16                | 1/0              |                                                        |                        |

| P12, P10                |                  | DDOM made setting pin De fixed at levelous             |                        |

| P22, P20                |                  | PROM mode setting pin. Be fixed at low level.          |                        |

| RESET                   |                  |                                                        |                        |

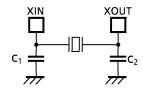

| XIN                     | Input            | Compared to CAMUS assistants at a hilling the internal | -1-1-                  |

| хоит                    | Output           | Connect an 8 MHz oscillator to stabilize the internal  | state.                 |

| VKK                     | VFT power supply | GND                                                    |                        |

| P97 to P90              | 1/0              |                                                        |                        |

| P87 to P80              | Output           |                                                        |                        |

| P77 to P70              |                  | Open                                                   |                        |

| P67 to P60              | 1/0              |                                                        |                        |

#### **Operational Description**

The following explains the TMP87PS71A hardware configuration and operation. The configuration and functions of the TMP87PS71A are the same as those of the TMP87CS71B, except in that a one-time PROM is used instead of an on-chip mask ROM.

The TMP87PS71A is placed in the *single-clock* mode during reset. To use the dual-clock mode, the low-frequency oscillator should be turned on by executing [SET (SYSCR2). XTEN] instruction at the beginning of the program.

# 1. Operating Mode

The TMP87PS71A has two modes: MCU and PROM.

#### 1.1 MCU Mode

The MCU mode is activated by fixing the TEST/VPP pin at low level.

In the MCU mode, operation is the same as with the TMP87CS71B (the TEST/VPP pin cannot be used open because it has no built-in pull-down resistance).

#### 1.1.1 Program Memory

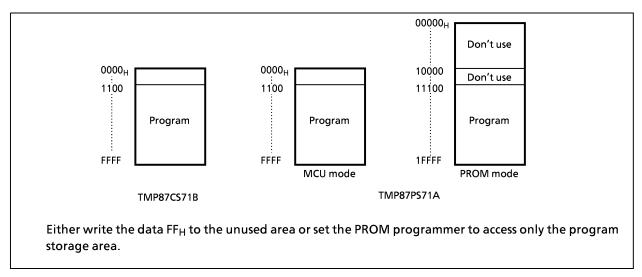

The TMP87PS71A has a 60 K  $\times$  8 bits (addresses 1100<sub>H</sub> to FFFF<sub>H</sub> in the MCU mode, addresses 11100<sub>H</sub> to 1FFFF<sub>H</sub> in the PROM mode) of program memory (OTP).

To use the TMP87PS71A as the system evaluation for the TMP87CS71B, the program should be written to the program memory area as shown in Figure 1-1.

Note: When accessing addresses 00000<sub>H</sub> to 110FF<sub>H</sub> of program memory in the PROM mode, blank, read or verify mode may not be guaranteed the operation; use addresses 11100<sub>H</sub> to 1FFFF<sub>H</sub>.

Figure 1-1. Program Memory Area

#### 1.1.2 Data Memory

The TMP87PS71A has an on-chip 2.0 K  $\times$  8 bits data memory (static RAM).

## **Electrical Characteristics**

**Absolute Maximum Ratings**

$(V_{SS} = 0 V)$

| Parameter                       | Symbol              | Conditions                  | Ratings                                       | Unit |  |

|---------------------------------|---------------------|-----------------------------|-----------------------------------------------|------|--|

| Supply Voltage                  | $V_{DD}$            |                             | - 0.3 to 6.5                                  | ٧    |  |

| Input Voltage                   | V <sub>IN</sub>     |                             | - 0.3 to V <sub>DD</sub> + 0.3                | ٧    |  |

| Output Valtage                  | V <sub>OUT1</sub>   | P2, P3, P4, P5, XOUT, RESET | - 0.3 to V <sub>DD</sub> + 0.3                | V    |  |

| Output Voltage                  | V <sub>OUT2</sub>   | Source open drain ports     | V <sub>DD</sub> – 40 to V <sub>DD</sub> + 0.3 | ]    |  |

|                                 | I <sub>OUT1</sub>   | P0, P1, P2, P3, P4, P5      | 3.2                                           |      |  |

| Output Current (Per 1 pin)      | I <sub>OUT3</sub>   | P8, P9 (segment outputs)    | - 12                                          | mA   |  |

|                                 | I <sub>OUT4</sub>   | P6, P7 (digit outputs)      | - 25                                          | ]    |  |

| O to 15 const (Total)           | Σ I <sub>OUT1</sub> | P0, P1, P2, P3, P4, P5      | 120                                           |      |  |

| Output Current (Total)          | Σ I <sub>OUT2</sub> | P6, P7, P8, P9              | - 120                                         | mA   |  |

| Power Dissipation [Topr = 70°C] | PD                  |                             | 350                                           | mW   |  |

| Soldering Temperature (time)    | Tsld                |                             | 260 (10 s)                                    | °C   |  |

| Storage Temperature             | Tstg                |                             | – 55 to 125                                   | °C   |  |

| Operating Temperature           | Topr                |                             | - 30 to 70                                    | °C   |  |

Note: The absolute maximum ratings are rated values which must not be exceeded during operation, even for an instant. Any one of the ratings must not be exceeded. If any absolute maximum rating is exceeded, a device may break down or its performance may be degraded, causing it to catch fire or explode resulting in injury to the user. Thus, when designing products which include this device, ensure that no absolute maximum rating value will ever be exceeded.

**Recommended Operating Conditions**

$(V_{SS} = 0V, Topr = -30 to 70^{\circ}C)$

| Parameter          | Symbol            | Pins                    |                           | Conditions             | Min                    | Max                    | Unit   |

|--------------------|-------------------|-------------------------|---------------------------|------------------------|------------------------|------------------------|--------|

|                    |                   |                         | fa ONALI-                 | NORMAL1, 2 mode        | 4.5                    |                        |        |

| Supply Voltage     |                   |                         | fc = 8 MHz                | IDLE1, 2 modes         | 4.5                    |                        |        |

|                    | $V_{DD}$          |                         | fs =                      | SLOW mode              | 2.7                    | 5.5                    | V V    |

|                    |                   |                         | 32.768 kHz                | SLEEP mode             | 2.7                    |                        |        |

|                    |                   |                         |                           | STOP mode              | 2.0                    |                        |        |

| Output Voltage     | V <sub>OUT3</sub> | Source open drain ports |                           |                        | V <sub>DD</sub> – 38   | V <sub>DD</sub>        | V      |

|                    | V <sub>IH1</sub>  | Except hysteresis input | $V_{DD} \ge 4.5 V$        |                        | $V_{DD} \times 0.70$   | V <sub>DD</sub>        | \<br>\ |

| Input High Voltage | V <sub>IH2</sub>  | Hysteresis input        |                           |                        | V <sub>DD</sub> × 0.75 |                        |        |

|                    | V <sub>IH3</sub>  |                         | V                         | / <sub>DD</sub> <4.5 V | V <sub>DD</sub> × 0.90 | V <sub>DD</sub>        |        |

|                    | V <sub>IL1</sub>  | Except hysteresis input | ,                         | / > A E \/             |                        | $V_{DD} \times 0.30$   |        |

| Input Low Voltage  | V <sub>IL2</sub>  | Hysteresis input        | V <sub>DD</sub> ≧ 4.5 V 0 |                        | V <sub>DD</sub> × 0.25 | V                      |        |

|                    | V <sub>IL3</sub>  |                         | V <sub>DD</sub> <4.5 V    |                        |                        | V <sub>DD</sub> × 0.10 |        |

| Clask Fraguency    | fc                | XIN, XOUT               | VDD                       | ) = 4.5 to 5.5V        | 0.4                    | 8.0                    | MHz    |

| Clock Frequency    | fs                | XTIN, XTOUT             |                           |                        | 30.0                   | 34.0                   | kHz    |

Note 1: The recommended operating conditions for a device are operating conditions under which it can be guaranteed that the device will operate as specified. If the device is used under operating conditions other than the recommended operating conditions (supply voltage, operating temperature range, specified AC/DC values etc.), malfunction may occur. Thus, when designing products which include this device, ensure that the recommended operating conditions for the device are always adhered to.

Note 2: Clock frequency fc: Supply voltage range is specified in NORMAL1/2 mode and IDLE1/2 mode.

DC Characteristics

$(V_{SS} = 0 \text{ V}, \text{ Topr} = -30 \text{ to } 70^{\circ}\text{C})$

| Parameter                           | Symbol                                                    | Pins                                                            | Conditions                                               | Min | Тур.                                                                                                | Max | Unit |

|-------------------------------------|-----------------------------------------------------------|-----------------------------------------------------------------|----------------------------------------------------------|-----|-----------------------------------------------------------------------------------------------------|-----|------|

| Hysteresis Voltage                  | $V_{HS}$                                                  | Hysteresis input                                                |                                                          | -   | 0.9                                                                                                 | _   | ٧    |

|                                     | I <sub>IN1</sub>                                          | TEST                                                            |                                                          |     |                                                                                                     |     |      |

| Input Current                       | I <sub>IN2</sub>                                          | Open drain ports,<br>Tri-state ports                            | V <sub>DD</sub> = 5.5 V<br>V <sub>IN</sub> = 5.5 V/0 V   | -   | _                                                                                                   | ± 2 | μΑ   |

|                                     | I <sub>IN3</sub>                                          | RESET, STOP                                                     |                                                          |     | - 0.9 - ±2  30 70 150  00 220 450  - 80 -  - 2  2  2  2  12  20  - 12 20  - 12 20  - 30 60  - 15 30 |     |      |

| Innut Bosistones                    | R <sub>IN1</sub>                                          | Port P4 with pull-down                                          |                                                          | 30  | 70                                                                                                  | 150 |      |

| Input Resistance                    | R <sub>IN2</sub>                                          | RESET                                                           |                                                          | 100 | 220                                                                                                 | 450 | kΩ   |

| Pull-down Resistance                | R <sub>K</sub>                                            | Source open drain ports                                         | $V_{DD} = 5.5 \text{ V}, V_{KK} = -30 \text{ V}$         | -   | 80                                                                                                  | _   |      |

|                                     | I <sub>LO1</sub>                                          | Sink open drain ports                                           | V <sub>DD</sub> = 5.5 V, V <sub>OUT</sub> = 5.5 V        | -   | _                                                                                                   | 2   |      |

| Output Leakage<br>Current           | I <sub>LO2</sub>                                          | Source open drain ports                                         | $V_{DD} = 5.5 \text{ V}, \ V_{OUT} = -32 \text{ V}$      | -   | -                                                                                                   | - 2 | μΑ   |

| Carrent                             | $I_{LO3}$ Tri-state ports $V_{DD} = 5.5 \text{ V}, V_{O}$ | $V_{DD} = 5.5 \text{ V}, \ V_{OUT} = 5.5 \text{ V}/0 \text{ V}$ | -                                                        | -   | ± 2                                                                                                 |     |      |

| Output High Valtage                 | V <sub>OH2</sub>                                          | Tri-state ports                                                 | $V_{DD} = 4.5 \text{ V}, I_{OH} = -0.7 \text{ mA}$       | 4.1 | _                                                                                                   | _   | v    |

| Output High Voltage                 | V <sub>OH3</sub>                                          | P8, P9                                                          | $V_{DD} = 4.5 \text{ V}, I_{OH} = -5 \text{ mA}$         | 2.4 | _                                                                                                   | _   | V    |

| Output Low Voltage                  | $V_{OL}$                                                  | Except XOUT                                                     | $V_{DD} = 4.5 \text{ V}, I_{OL} = 1.6 \text{ mA}$        | -   | -                                                                                                   | 0.4 | V    |

| Output High current                 | I <sub>OH</sub>                                           |                                                                 | $V_{DD} = 4.5 \text{ V}, V_{OH} = 2.4 \text{ V}$         | -   | - 15                                                                                                | _   | mA   |

| Supply Current in NORMAL 1, 2 modes |                                                           |                                                                 | V <sub>DD</sub> = 5.5 V<br>fc = 8 MHz                    | _   | 12                                                                                                  | 20  |      |

| Supply Current in IDLE 1, 2 modes   |                                                           |                                                                 | fs = 32.768 kHz<br>V <sub>IN</sub> = 5.3 V/0.2 V         | -   | 6                                                                                                   | 10  | mA   |

| Supply Current in SLOW mode         | I <sub>DD</sub>                                           |                                                                 | V <sub>DD</sub> = 3.0 V                                  | -   | 30                                                                                                  | 60  | _    |

| Supply Current in<br>SLEEP mode     |                                                           |                                                                 | fs = 32.768 kHz<br>V <sub>IN</sub> = 2.8 V/0.2 V         | -   | 15                                                                                                  | 30  | μΑ   |

| Supply Current in STOP mode         |                                                           |                                                                 | V <sub>DD</sub> = 5.5 V<br>V <sub>IN</sub> = 5.3 V/0.2 V | _   | 0.5                                                                                                 | 10  | μΑ   |

Note 1: Typical values show those at Topr = 25°C ,  $V_{DD}$  = 5 V.

Note 2: Input Current I<sub>IN1</sub>, I<sub>IN3</sub>; The current through resistor is not included, when the input resistor (pull-upor pull-down) is contained.

Note 3: Typical current consumption during AD conversion is 1.2 mA.

**AD Conversion Characteristics**

$(V_{SS} = 0 \text{ V}, V_{DD} = 4.5 \text{ to } 5.5 \text{ V}, Topr = -30 \text{ to } 70^{\circ}\text{C})$

| Parameter                  | Symbol           | Pins         | Conditions               | Min             | Тур. | Max      | Unit |

|----------------------------|------------------|--------------|--------------------------|-----------------|------|----------|------|

| Analog Input Voltage Range | V <sub>CIN</sub> | CIN5 to CIN0 |                          | V <sub>SS</sub> | -    | $V_{DD}$ | ٧    |

| Conversion Error           |                  |              | $V_{DD} = 5.0 \text{ V}$ | -               | -    | ± 1.5    | LSB  |

#### **AC Characteristics**

$(V_{SS} = 0 \text{ V}, V_{DD} = 2.7/4.5 \text{ to } 5.5 \text{ V}, \text{ Topr} = -30 \text{ to } 70^{\circ}\text{C})$

| Parameter                    | Symbol           | Conditions                    | Min   | Тур. | Max   | Unit |

|------------------------------|------------------|-------------------------------|-------|------|-------|------|

|                              |                  | In NORMAL1, 2 modes           | ٥٠    |      | 10    |      |

| Mashina Cuda Tina            |                  | In IDLE1, 2 modes             | 0.5   | _    |       | μ\$  |

| Machine Cycle Time           | t <sub>cy</sub>  | In SLOW mode                  | 117.6 |      | 133.3 |      |

|                              |                  | In SLEEP mode                 | 117.6 | _    |       |      |

| High Level Clock Pulse Width | t <sub>WCH</sub> | For external clock operation  | F0    |      |       |      |

| Low Level Clock Pulse Width  | t <sub>WCL</sub> | (XIN input), fc = 8 MHz       | 50    | _    | _     | ns   |

| High Level Clock Pulse Width | t <sub>WSH</sub> | For external clock operation  | 14.7  |      |       |      |

| Low Level Clock Pulse Width  | t <sub>WSL</sub> | (XTIN input), fs = 32.768 kHz | 14.7  | ı    | _     | μ\$  |

# **Recommended Oscillating Conditions**

$$(V_{SS} = 0 \text{ V}, V_{DD} = 2.7/4.5 \text{ to } 5.5 \text{ V}, \text{ Topr} = -30 \text{ to } 70^{\circ}\text{C})$$

(1) High-frequency Oscillation

(2) Low-frequency Oscillation

- Note 1: An electrical shield by metal shield plate on the surface of the IC package should be recommendable in order to prevent the device from the high electric fieldstress applied for continuous reliable operation.

- Note 2: The product numbers and specifications of the resonators by Murata Manufacturing Co., Ltd. are subject to change.

For up-to-date information, please refer to the following URL;

http://www.murata.co.jp/search/index.html

DC/AC Characteristics (PROM mode)

$(V_{SS} = 0 V)$

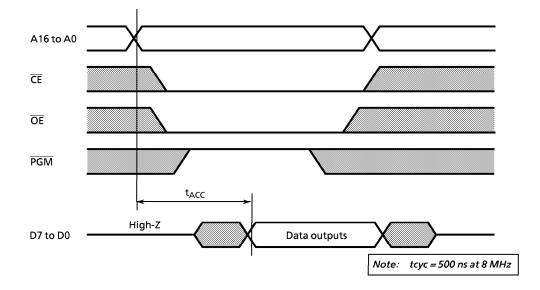

# (1) Read Operation

| Parameter                    | Symbol           | Conditions                     | Min  | Тур.           | Max             | Unit |

|------------------------------|------------------|--------------------------------|------|----------------|-----------------|------|

| Input High Voltage           | V <sub>IH4</sub> |                                | 2.2  | -              | V <sub>CC</sub> | V    |

| Input Low Voltage            | V <sub>IL4</sub> |                                | 0    | -              | 0.8             | V    |

| Power Supply Voltage         | V <sub>CC</sub>  |                                | 4.75 | 5.0            | 5.25            | v    |

| Program Power Supply Voltage | $V_{PP}$         |                                | 4.73 | 3.0            | 3.23            | V    |

| Address Access Time          | T <sub>ACC</sub> | V <sub>CC</sub> = 5.0 ± 0.25 V | _    | 1.5 tcyc + 300 |                 | ns   |

Note: tcyc = 500 ns at 8 MHz

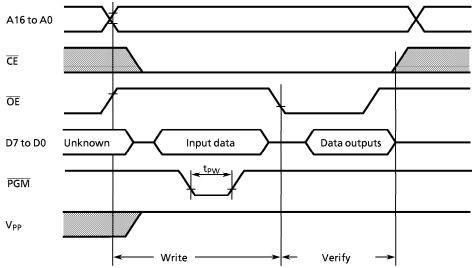

#### (2) Program Operation (High-Speed program mode) (Topr = $25 \pm 5^{\circ}$ C)

| Parameter                    | Symbol           | Conditions                                             | Min   | Тур.  | Max             | Unit     |

|------------------------------|------------------|--------------------------------------------------------|-------|-------|-----------------|----------|

| Input High Voltage           | V <sub>IH4</sub> |                                                        | 2.2   | -     | V <sub>CC</sub> | ٧        |

| Input Low Voltage            | V <sub>IL4</sub> |                                                        | 0     | -     | 0.8             | ٧        |

| Power Supply Voltage         | V <sub>CC</sub>  |                                                        | 6.00  | 6.25  | 6.5             | <b>V</b> |

| Program Power Supply Voltage | V <sub>PP</sub>  |                                                        | 12.5  | 12.75 | 13.0            | <b>V</b> |

| Initial Program Pulse Width  | t <sub>PW</sub>  | $V_{CC} = 6.25 \text{ V}$<br>$V_{PP} = 12.75 \pm 0.25$ | 0.095 | 0.1   | 0.105           | ms       |

- Note 1:When  $V_{cc}$  power supply is turned on or after,  $V_{pp}$  must be increased. When  $V_{cc}$  power supply is turned off or before,  $V_{pp}$  must be decreased.

- Note 2: The device must not be set to the EPROM programmer or picked up from it under applying the program voltage (12.5 V  $\pm$  0.5 V = V) to the  $V_{pp}$  pin as the device is damaged.

- Note 3:Do not apply the parameter of program voltage (more than + 13 V) including overshoot to the  $V_{\text{DD}}$  pin.

- Note 4:Be sure to execute the recommended programing mode with the recommended programing adaptor. If a mode or an adaptor except the above, the misoperation sometimes occurs.