November 1987

#### **Description**

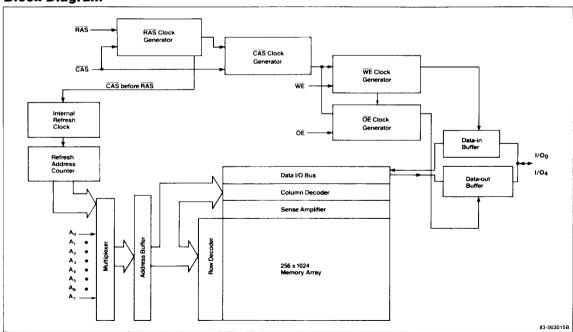

The  $\mu$ PD41464 is a 65,536-word by 4-bit dynamic N-channel MOS random access memory (RAM) designed to operate from a single +5-volt power supply. The negative voltage substrate bias is generated internally; its operation is automatic and transparent. The  $\mu$ PD41464 utilizes double-polylayer, N-channel silicon gate processing, which provides high storage cell density, high performance, and high reliability. The device also uses a single-transistor dynamic storage cell and advanced dynamic circuitry throughout, ensuring minimum power dissipation.

The three-state I/O is controlled by  $\overline{CAS}$  independent of  $\overline{RAS}$ . After a valid read or hidden refresh cycle, data is held on the I/O by holding  $\overline{CAS}$  low. The data I/O is returned to the high-impedance state by returning  $\overline{CAS}$  high. The  $\mu$ PD41464 hidden refresh feature allows  $\overline{CAS}$  to be held low to maintain output data while  $\overline{RAS}$  is used to execute  $\overline{RAS}$ -only refresh cycles.

Refresh is accomplished by using  $\overline{CAS}$  before  $\overline{RAS}$  cycles, enabling the internal generation of the refresh address. Refresh can also be accomplished by using  $\overline{RAS}$ -only refresh or normal read or write cycles on the 256 address combinations of  $A_0$ - $A_7$  during the 4-ms refresh period.

#### **Features**

- ☐ 65,536-word by 4-bit organization

- ☐ Single +5-volt ±10% power supply

- ☐ CAS before RAS internal address refresh mode

☐ Multiplexed address inputs

- ☐ On-chip substrate bias generator

- ☐ Low power dissipation

- 28 mW (standby)

- 440 mW (active,  $t_{RC} = t_{RC}$  min)

- ☐ Nonlatched TTL-compatible I/O

- ☐ Low input capacitance

- ☐ 256 refresh cycles during 4-ms period

- ☐ Standard plastic DIP, PLCC, and ZIP packages

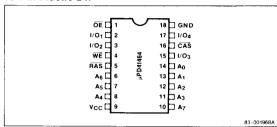

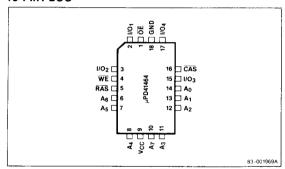

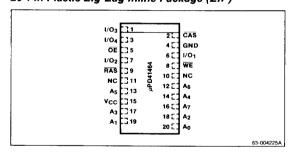

#### Pin Configurations

#### 18-Pin Plastic DIP

#### 18-Pin PLCC

#### 20-Pin Plastic Zig-Zag Inline Package (ZIP)

#### Pin Identification

| Symbol                         | Function              |

|--------------------------------|-----------------------|

| A <sub>0</sub> -A <sub>7</sub> | Address inputs        |

| 1/01-1/04                      | Data I/O              |

| RAS                            | Row address strobe    |

| CAS                            | Column address strobe |

| WE                             | Write enable          |

| ŌĒ                             | Output enable         |

| GND                            | Ground                |

| V <sub>CC</sub>                | Power supply          |

| NC                             | No connection         |

| <del></del>                    |                       |

#### **Absolute Maximum Ratings**

| Voltage on any pin relative to GND            | -1.0 to +7.0 V |

|-----------------------------------------------|----------------|

| Operating temperature. T <sub>OPR</sub>       | 0 to +70°C     |

| Storage temperature, T <sub>STG</sub>         | −55 to +125°C  |

| Short-circuit output current, I <sub>OS</sub> | 50 mA          |

| Power dissipation, P <sub>D</sub>             | 1 W            |

Comment: Exposure to Absolute Maximum Ratings for extended periods may affect device reliability; exceeding the ratings could cause permanent damage. The device should be operated within the limits specified under DC and AC Characteristics.

#### **Ordering Information**

| Part Number  | Row Access<br>Time (Max) | Package            |

|--------------|--------------------------|--------------------|

| μPD41464C-10 | 100 ns                   | 18-pin plastic DIP |

| C-12         | 120 ns                   | <del>-</del> .     |

| C-15         | 150 ns                   | _                  |

| μPD41464L-10 | 100 ns                   | 18-pin PLCC        |

| L-12         | 120 ns                   | _                  |

| L-15         | 150 ns                   | <del>-</del>       |

| μPD41464V-10 | 100 ns                   | 20-pin ZIP         |

| V-12         | 120 ns                   | _                  |

| V-15         | 150 ns                   | _                  |

#### Capacitance

T<sub>A</sub> = 25 °C; f = 1 MHz

|                          |                 |     | Limit | В   |      | Pins Under Test                    |

|--------------------------|-----------------|-----|-------|-----|------|------------------------------------|

| Parameter                | Symbol          | Min | Тур   | Max | Unit |                                    |

| Input capacitance        | C <sub>l1</sub> |     |       | 5   | pF   | A <sub>0</sub> -A <sub>7</sub>     |

| Input capacitance        | C <sub>12</sub> |     |       | 8   | pF   | RAS, CAS, WE, OE                   |

| Input/output capacitance | C <sub>0</sub>  |     | ·     | 7   | pF   | 1/0 <sub>1</sub> -1/0 <sub>4</sub> |

## **Block Diagram**

#### **DC Characteristics**

$T_A = 0 \text{ to } +70 \,^{\circ}\text{C}; V_{CC} = 5.0 \text{ V} \pm 10\%$

|                        |                   |      | Limits |                 |      | Test                                                       |  |

|------------------------|-------------------|------|--------|-----------------|------|------------------------------------------------------------|--|

| Parameter              | Symbol            | Min  | Тур    | Max             | Unit | Conditions                                                 |  |

| Supply voltage         | V <sub>CC</sub>   | 4.5  | 5.0    | 5.5             | ٧    | Referenced to GND                                          |  |

| Input voltage, high    | V <sub>IH</sub>   | 2.4  |        | 5.5             | ٧    | Referenced to GND                                          |  |

| Input voltage, low     | VIL               | -1.0 |        | 0.8             | ٧    | Referenced to GND                                          |  |

| Standby current        | I <sub>CC2</sub>  |      |        | 5.0             | mA   | $\overline{RAS} = \overline{CAS} = V_{1H}$                 |  |

| Input leakage current  | l <sub>I(L)</sub> | -10  |        | 10              | μΑ   | $V_{IN} = 0$ to 5.5 V, all other pins not under test = 0 V |  |

| Output leakage current | 1 <sub>0(L)</sub> | -10  |        | 10              | μΑ   | I/O is High-Z, $V_{I/O} = 0$ to 5.5 V                      |  |

| Output voltage, low    | V <sub>OL</sub>   | 0    |        | 0.4             | ٧    | $I_{OL} = 4.2 \text{ mA}$                                  |  |

| Output voltage, high   | V <sub>OH</sub>   | 2.4  |        | V <sub>CC</sub> | ٧    | $I_{OH} = -5 \text{ mA}$                                   |  |

AC Characteristics  $T_A = 0$  to +70 °C;  $V_{CC} = 5.0$  V  $\pm 10\%$

| Parameter                                                     | Symbol           | µPD41464-10 |       | μ <b>PD41464-12</b> |       | μ <b>PD41464</b> -15 |       |      | Test                                                                                 |

|---------------------------------------------------------------|------------------|-------------|-------|---------------------|-------|----------------------|-------|------|--------------------------------------------------------------------------------------|

|                                                               |                  | Min         | Max   | Min                 | Max   | Min                  | Max   | Unit | Conditions                                                                           |

| Operating current, average                                    | I <sub>CC1</sub> |             | 80    |                     | 75    |                      | 70    | mA   | $\overline{RAS}$ , $\overline{CAS}$ cycling, $t_{RC} = t_{RC}$ min (Note 5)          |

| Operating current, refresh mode, average                      | Іссз             |             | 65    | ***                 | 60    |                      | 55    | mA   | $\overline{RAS}$ cycling, $\overline{CAS} = V_{IH}$ , $t_{RC} = t_{RC}$ min (Note 5) |

| Operating current, page mode, average                         | ICC4             |             | 55    |                     | 50    |                      | 45    | mA   | $\overline{RAS} = V_{IL}$ , $\overline{CAS}$ cycling, $t_{PC} = t_{PC}$ min (Note 5) |

| Operating current, CAS<br>before RAS refresh mode,<br>average | I <sub>CC5</sub> |             | 70    |                     | 65    |                      | 60    | mA   | $\overline{RAS}$ cycling, $\overline{CAS} = V_{IL}$ , $t_{RC} = t_{RC}$ min (Note 5) |

| Random read or write cycle time                               | t <sub>RC</sub>  | 200         |       | 220                 |       | 260                  |       | ns   | (Note 6)                                                                             |

| Read-write cycle time                                         | tRWC             | 270         |       | 300                 |       | 355                  |       | ns   | (Note 6)                                                                             |

| Page mode cycle time                                          | tpc              | 100         |       | 120                 | -     | 145                  |       | ns   | (Note 6)                                                                             |

| Refresh period                                                | tREF             |             | 4     |                     | 4     |                      | 4     | ms   |                                                                                      |

| Access time from RAS                                          | tRAC             |             | 100   |                     | 120   |                      | 150   | ns   | (Notes 7, 8)                                                                         |

| Access time from CAS                                          | tCAC             | ***         | 50    |                     | 60    |                      | 75    | ns   | (Notes 7, 9)                                                                         |

| Output buffer turn-off delay                                  | toff             | 0           | 25    | 0                   | 30    | 0                    | 40    | ns   | (Note 10)                                                                            |

| Transition time (rise and fall)                               | t <sub>T</sub>   | 3           | 50    | 3                   | 50    | 3                    | 50    | ns   | (Note 3)                                                                             |

| RAS precharge time                                            | t <sub>RP</sub>  | 90          |       | 90                  |       | 100                  |       | ns   |                                                                                      |

| RAS pulse width                                               | tRAS             | 100         | 10000 | 120                 | 10000 | 150                  | 10000 | ns   |                                                                                      |

| RAS hold time                                                 | tash             | 50          |       | 60                  |       | 75                   |       | ns   |                                                                                      |

| CAS pulse width                                               | t <sub>CAS</sub> | 50          | 10000 | 60                  | 10000 | 75                   | 10000 | ns   |                                                                                      |

| CAS hold time                                                 | tcsH             | 100         |       | 120                 |       | 150                  |       | ns   |                                                                                      |

| RAS to CAS delay time                                         | tRCD             | 20          | 50    | 25                  | 60    | 25                   | 75    | ns   | (Note 11)                                                                            |

| CAS to RAS precharge time                                     | tCRP             | 10          |       | 10                  |       | 10                   |       | ns   | (Note 12)                                                                            |

| CAS precharge time, non-page cycle                            | tCPN             | 25          |       | 25                  |       | 25                   |       | ns   |                                                                                      |

| CAS precharge time, page cycle                                | t <sub>CP</sub>  | 40          |       | 50                  |       | 60                   |       | ns   |                                                                                      |

# **AC Characteristics (cont)**

| Parameter                                             | Symbol           | μ <b>PD41464-1</b> 0 |     | μPD41464-12 |     | μ <b>PD41464-15</b> |     |      | Test       |

|-------------------------------------------------------|------------------|----------------------|-----|-------------|-----|---------------------|-----|------|------------|

|                                                       |                  | Min                  | Max | Min         | Max | Min                 | Max | Unit | Conditions |

| RAS precharge CAS<br>hold time                        | t <sub>RPC</sub> | 0                    |     | 0           |     | 0                   |     | ns   |            |

| Row address setup time                                | tasa             | 0                    |     | 0           |     | 0                   |     | ns   |            |

| Row address hold time                                 | tRAH             | 10                   |     | 15          |     | 15                  |     | ns   |            |

| Column address setup<br>time                          | t <sub>ASC</sub> | 0                    |     | 0           |     | 0                   |     | ns   |            |

| Column address hold<br>time                           | t <sub>CAH</sub> | 15                   |     | 20          |     | 25                  |     | ns   |            |

| Column address ho <u>ld</u><br>time referenced to RAS | t <sub>AR</sub>  | 65                   |     | 80          | _   | 100                 |     | ns   |            |

| Read command setup<br>time                            | t <sub>RCS</sub> | 0                    |     | 0           |     | 0                   |     | ns   |            |

| Read command ho <u>ld</u><br>time referenced to RAS   | t <sub>RRH</sub> | 10                   |     | 10          |     | 10                  |     | ns   | (Note 13)  |

| Read command hold<br>time referenced to CAS           | <sup>t</sup> RCH | 0                    |     | 0           |     | 0                   |     | ns   | (Note 13)  |

| Write command hold<br>time                            | twcH             | 25                   |     | 30          |     | 40                  |     | ns   |            |

| Write command hold<br>time referenced to RAS          | twcr             | 75                   |     | 90          |     | 115                 |     | ns   |            |

| Write command pulse width                             | t <sub>WP</sub>  | 15                   |     | 20          |     | 25                  |     | ns   |            |

| Write command to RAS<br>lead time                     | t <sub>RWL</sub> | 35                   |     | 40          |     | 45                  |     | ns   |            |

| Write command to CAS<br>lead time                     | tcwL             | 35                   |     | 40          |     | 45                  |     | ns   |            |

| Data-in setup time                                    | t <sub>DS</sub>  | 0                    |     | 0           |     | 0                   |     | ns   | (Note 14)  |

| Data-in hold time                                     | t <sub>DH</sub>  | 25                   |     | 30          |     | 40                  |     | ns   | (Note 14)  |

| Data-in hold time<br>referenced to RAS                | t <sub>DHR</sub> | 75                   |     | 90          |     | 115                 | _   | ns   |            |

| Write command setup<br>time                           | twcs             | 0                    |     | 0           |     | 0                   |     | ns   | (Note 15)  |

| RAS to WE delay                                       | t <sub>RWD</sub> | 130                  |     | 155         |     | 195                 |     | ns   | (Note 15)  |

| CAS to WE delay                                       | tcwp             | 80                   |     | 95          |     | 120                 |     | ns   | (Note 15)  |

| Access time from OE                                   | t <sub>OEA</sub> |                      | 25  |             | 30  |                     | 40  | пѕ   |            |

| Data delay time                                       | toED             | 25                   |     | 30          |     | 40                  |     | ns   |            |

| DE command hold time                                  | toeh             | 0                    |     | 0           |     | 0                   |     | ns   |            |

| Output turn-off delay<br>rom OE                       | t <sub>OEZ</sub> | 0                    | 25  | 0           | 30  | 0                   | 40  | ns   |            |

| DE to RAS inactive setup ime                          | t <sub>OES</sub> | 10                   |     | 10          |     | 10                  |     | ns   |            |

| CAS setup time for<br>CAS before RAS refresh          | t <sub>CSR</sub> | 10                   |     | 10          |     | 10                  |     | ns   |            |

| CAS hold time for CAS<br>before RAS refresh           | tchr             | 20                   |     | 25          | -   | 30                  |     | ns   |            |

#### Notes:

- (1) An initial pause of 100  $\mu$ s (RAS inactive) is required after power-up, followed by any 8 RAS cycles, before proper device operation is achieved.

- AC measurements assume t<sub>T</sub> = 5 ns.

- (3) VIH (min) and VIL (max) are reference levels for measuring timing of input signals.

- (4) All voltages referenced to GND.

- (5) I<sub>CC1</sub>, I<sub>CC3</sub>, I<sub>CC4</sub>, and I<sub>CC5</sub> depend on output loading and cycle rates. Specified values are obtained with the output open. For lot code K of µPD41464-15, t<sub>RC</sub> min must be 270 ns and I<sub>CC3</sub> = 60 mA.

- (6) The minimum specifications are used only to indicate the cycle time at which proper operation over the full temperature range (T<sub>A</sub> = 0 to +70°C) is assured. For lot code K of μPD41464-15, t<sub>RC</sub> min must be 270 ns.

- (7) Load = 2 TTL loads and 100 pF

- (8) Assumes that t<sub>RCD</sub> ≤ t<sub>RCD</sub> (max). If t<sub>RCD</sub> is greater than the maximum recommended value in this table, t<sub>RAC</sub> increases by the amount that t<sub>RCD</sub> exceeds the value shown.

- (9) Assumes that t<sub>RCD</sub> ≥ t<sub>RCD</sub> (max).

- (10) t<sub>OFF</sub> (max) and t<sub>OFZ</sub> (max) define the time at which the outputs achieve the open circuit condition and are not referenced to V<sub>OH</sub> or V<sub>OL</sub>.

- (11) Operation within the t<sub>RCD</sub> (max) limit assures that t<sub>RAC</sub> (max) can be met. t<sub>RCD</sub> (max) is specified as a reference point only; if t<sub>RCD</sub> is greater than t<sub>RCD</sub> (max), access time is controlled exclusively by t<sub>CAC</sub>.

- (12) The t<sub>CRP</sub> requirement should be applicable for RAS/CAS cycles preceded by any cycle.

- (13) Either tare or tach must be satisfied for a read cycle.

- (14) These parameters are referenced to the leading edge of CAS for early write cycles and to the leading edge of WE for delayed write or read-modify-write cycles.

- (15) t<sub>WCS</sub>, t<sub>CWD</sub>, and t<sub>RWD</sub> are restrictive operating parameters in read-write/read-modify-write cycles only. If t<sub>WCS</sub>≥t<sub>WCS</sub> (min), the cycle is an early write cycle and the data I/O pins will remain high impedance throughout the entire cycle. If t<sub>CWD</sub>≥t<sub>CWD</sub> (min) and t<sub>RWD</sub>≥t<sub>RWD</sub> (min), the cycle is a read-write cycle and the data I/O pins will contain data read from the selected cells. If neither of the above conditions is met, the condition of the data I/O pins (at access time and until CAS returns to V<sub>IH</sub>) is indeterminate.

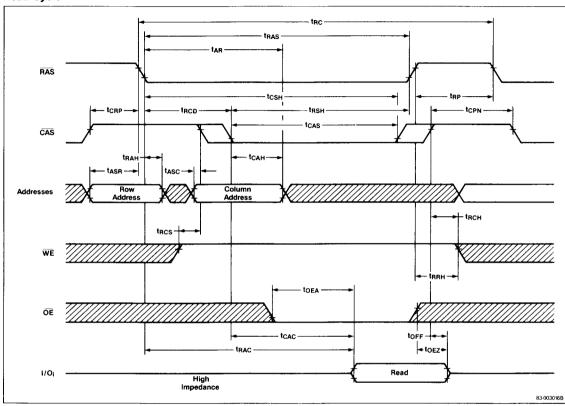

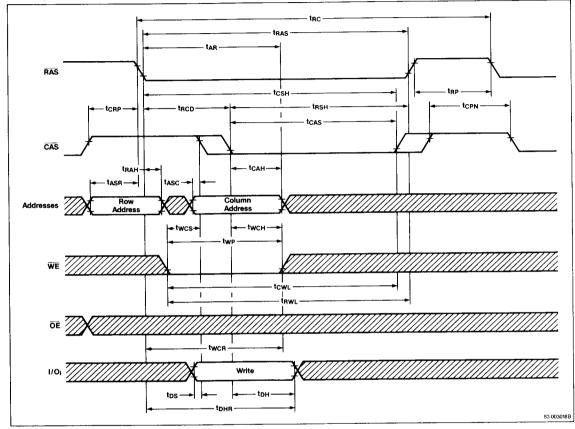

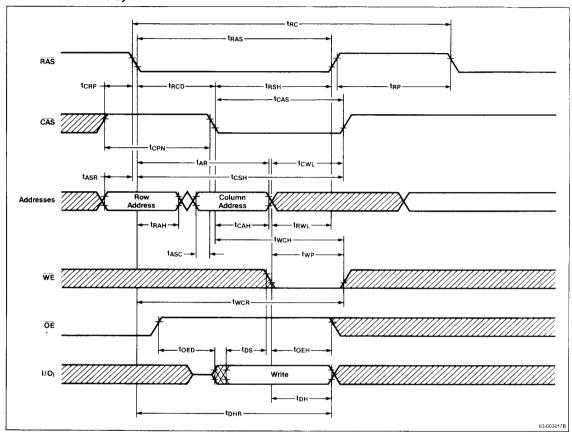

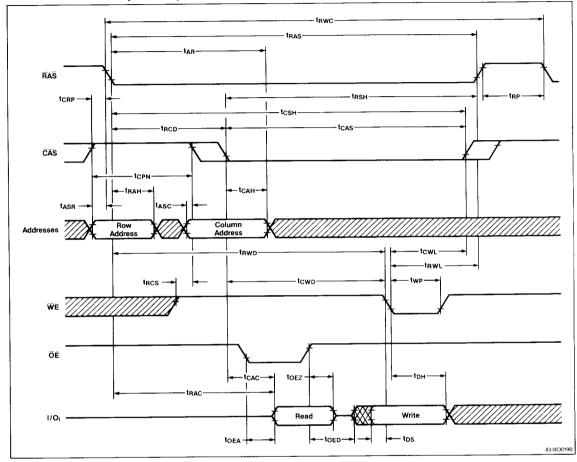

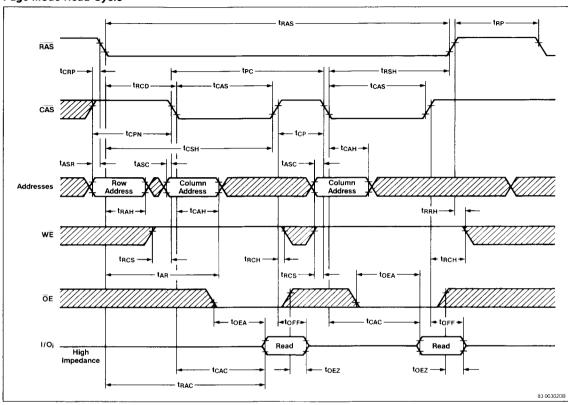

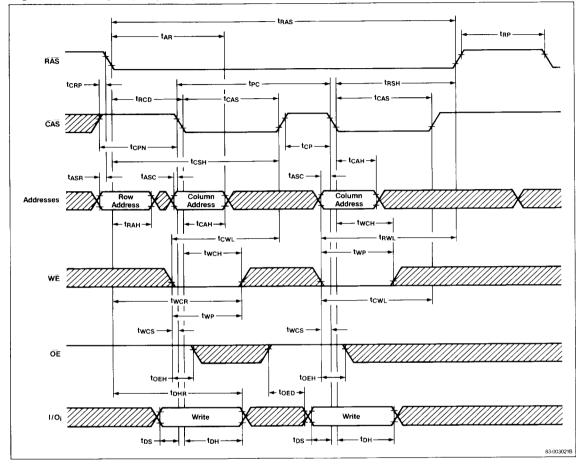

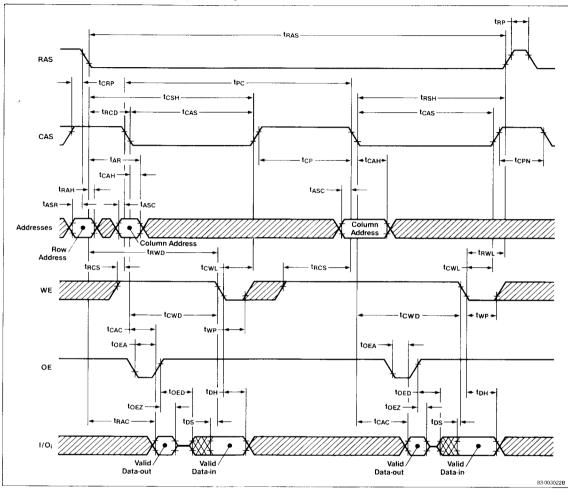

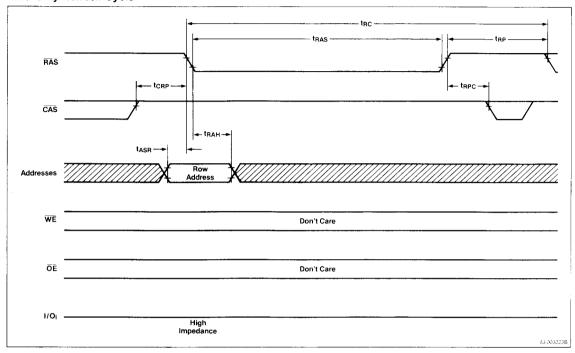

# **Timing Waveforms**

# Read Cycle

## Write Cycle (Early Write)

# **OE**-Controlled Write Cycle

#### Read-Write/Read-Modify-Write Cycle

## Page Mode Read Cycle

#### Page Mode Write Cycle (Early Write)

# Page Mode Read-Write/Read-Modify-Write Cycle

# RAS-Only Refresh Cycle

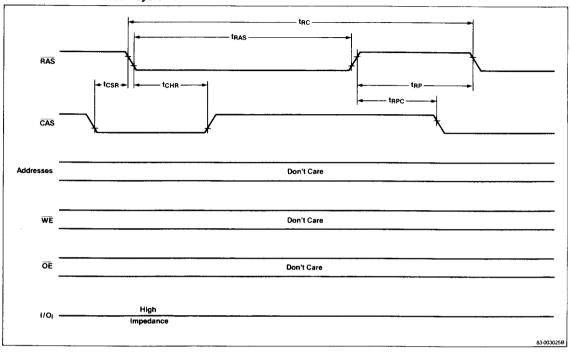

# CAS Before RAS Refresh Cycle

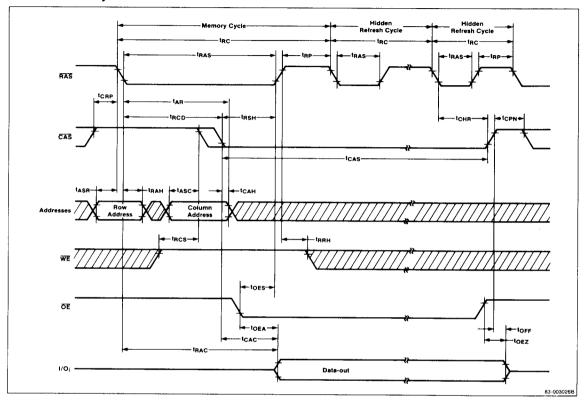

#### Hidden Refresh Cycle

#### **Package Drawings**

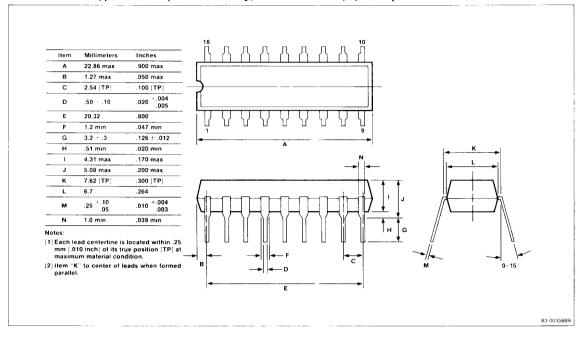

#### 18-Pin Plastic DIP, µPD41464C (Semiwide Body, Process Codes L, F, and N)

## Package Drawings (cont)

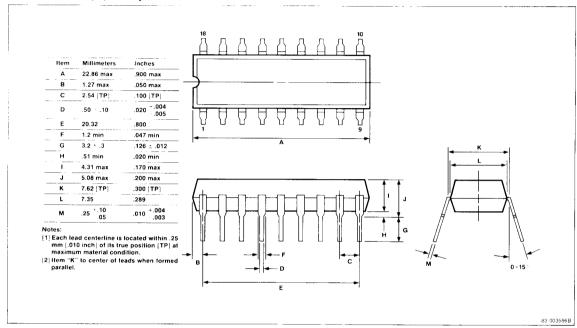

18-Pin Plastic DIP (300-mil, Wide Body, Process Code K; superseded by Semiwide Body, Process Codes L, F, and N)

## Package Drawings (cont)

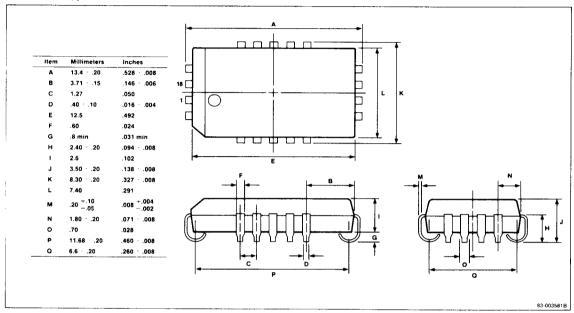

#### 18-Pin PLCC, µPD41464L

#### Package Drawings (cont)

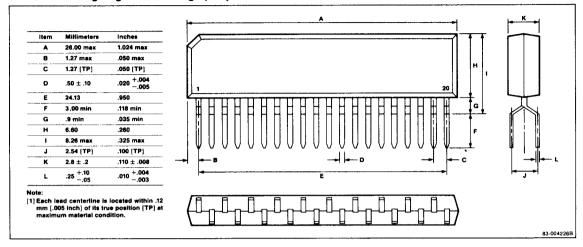

## 20-Pin Plastic Zig-Zag Inline Package (ZIP)

401 Ellis Street P.O. Box 7241 TEL 415-960-6000

Mountain View, CA 94039 TWX 910-379-6985

For Literature Call Toll Free: 1-800-632-3531

1-800-632-3532 (In California)

No part of this document may be copied or reproduced in any form or by any means without the prior written consent of NEC Electronics Inc. The information in this document is subject to change without notice. Devices sold by NEC Electronics Inc. are covered by the warranty and patent indemnification provisions appearing in NEC Electronics inc. Ferns and Conditions of Sale only. NEC Electronics Inc makes no warranty, express, statutory, implied, or by description, regarding the information set forth herein or regarding the freedom of the described devices from patent infringement. NEC Electronics Inc. makes no warranty of merchantability or fitness for any purpose. NEC Electronics Inc. assumes no responsibility for any errors that may appear in this document. NEC Electronics Inc. makes no commitment to update or to keep current the information contained in this document.

008470 1/2 1/2

NECEL-000450 STOCK NO. 600251