# **Z86E11**

# 4K EPROM, Z8 FAMILY MICROCOMPUTER

- COMPLETE MICROCOMPUTER

- 4K BYTES OF EPROM

- 128 BYTES OF RAM

- 32 I/O LINES

- UP TO 60K BYTES ADDRESSABLE EXTERNAL SPACE EACH FOR PROGRAM AND DATA MEMORY

- FULLY COMPATIBLE WITH STANDARD ROM VERSION

- 144-BYTE REGISTER FILE, INCLUDING 124 GENERAL PURPOSE REGISTERS, 4 I/O PORT REGISTERS, AND 16 STATUS AND CONTROL REGISTERS

- MINIMUM INSTRUCTION EXECUTION TIME 1µs, AT 12MHz

- VECTORED PRIORITY INTERRUPTS FOR I/O, COUNTER/TIMERS, AND UART

- FULL-DUPLEX UART AND TWO PROGRAMM-ABLE 8-BIT COUNTER/TIMERS, EACH WITH A 6-BIT PROGRAMMABLE PRESCALER

- REGISTER POINTER SO THAT SHORT, FAST INSTRUCTIONS CAN ACCESS ANY OF NINE WORKING-REGISTER GROUPS IN 1.5μs (8MHz)

- ON-CHIP OSCILLATOR WHICH ACCEPTS CRYSTAL OR EXTERNAL CLOCK DRIVE

- SINGLE + 5V POWER SUPPLY ALL PINS TTL COMPATIBLE

- THREE EPROM PROGRAMMING MODES:

- EPROM-LIKE, USING A STANDARD EPROM PROGRAMMER

- SELF PROGRAMMING DURING NORMAL PROGRAM EXECUTION

- AN OFF-CHIP EPROM PROVIDES A PRO-GRAM/VERIFY FACILITY TO ALLOW ASIMPLE AND TIME-EFFICIENT AUTO LOADING OPER-ATION

- INTEGRATED PROGRAMMABLE PROTEC-TIONS AVOID EPROM CONTENT READOUT

- AVAILABLE IN 8MHz AND 12MHz VERSIONS

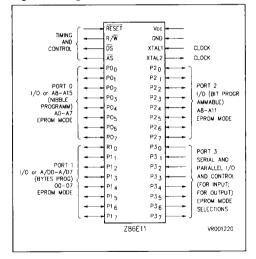

Figure 1: Logic Functions

August 1991

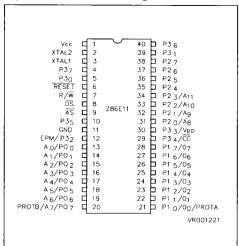

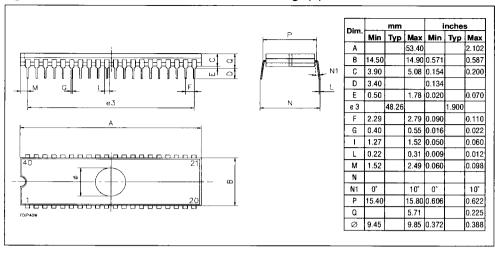

Figure 2: 40 Pins DIL Configuration.

#### **GENERAL DESCRIPTION**

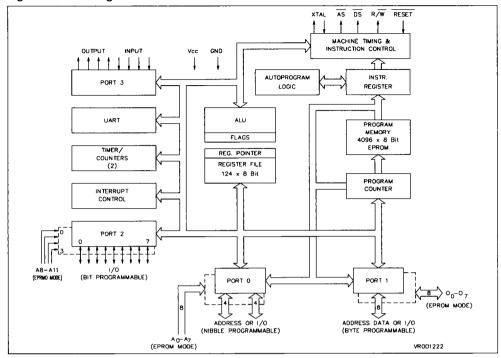

The Z86E11 microcomputer introduces a new level of sophistication to single-chip architecture. Compared to earlier single-chip microcomputers, the Z8 offers faster execution; more efficient use of memory; more sophisticated interrupt, input/output and bit-manipulation capabilities; and easier system expansion.

Under program control, the Z8 can be tailored to the needs of its user. It can be configured as a stand-alone microcomputer with 4K bytes of internal EPROM, a traditional microprocessor that manages up to 120K bytes of external memory, or a parallel-processing element in a system with other processors and peripheral controllers linked by the Z-BUS. In all configurations, a large number of pins remain available for I/O.

The 4Kx8 on-board EPROM can be programmed in three modes, Eprom-like, Self programming and Autoloading. In Eprom-like, the programming procedure is similar to that for a M2732 (using an

interface board), with the only exception being for the programming voltage which must be 12.5V related to the SGS-THOMSON NMOS-E3 used technology. Self-programming permits byte-programming during normal microcomputer program execution.

An important facility is the programmable readout protections which allows the user to inhibit external access to proprietary program code by programming 2 non-volatile transistors. These locks can be reset only by erasing the entire EPROM array. For its characteristics, the Z86E11 can be considered as a low cost development tool for the Z8 microcomputer family.

#### **ARCHITECTURE**

Z8 architecture is characterized by a flexible I/O scheme, an efficient register and address space structure and a number of ancillary features that are helpful in many applications.

Microcomputer applications demand powerful I/O capabilities. The Z8 fulfills this with 32 pins dedicated to input/output. These lines are grouped into four ports of eight lines each and are configurable under software control to provide timing, status signals, serial or parallel I/O with or without handshake, address/data bus for interfacing external memory.

Because the multiplexed address/data bus is merged with the I/O-oriented ports, the Z8 can assume many different memory and I/O configurations. These configurations range from a self-contained microcomputer to a microprocessor that can address 120K bytes of external memory (figure 4).

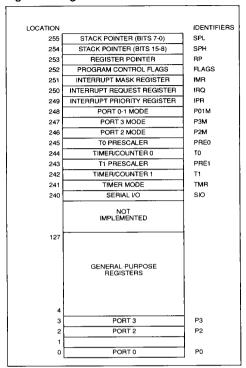

Three basic address spaces are available to support this wide range of configurations: program memory (internal and external), data memory (external) and the register file (internal). The 144-byte random-access register file is composed of 124 general-purpose registers, four I/O port registers, and 16 control and status registers.

To unburden the program from copying with realtime problems such as serial data communication and counting/timing, an asynchronous receiver/transmitter (UART) and two counter/timers with a large number of user-selectable modes are offered on-chip.

Hardware support for the UART is minimized because one of the on-chip timers supplies the bit rate.

# ARCHITECTURE (Continued)

Figure 3: Block Diagram

#### PIN DESCRIPTIONS

**P0<sub>0</sub>-P0<sub>7</sub>.** I/O Port Lines (input/outputs, TTL compatible). 8 lines nibble-programmable that can be configured under program control for I/O or external memory interface.

**P10-P17.** I/O Port Lines (input/outputs, TTL compatible). 8 lines byte programmable that can be configured under program control for I/O or multiplexed address ( $A_0$ - $A_7$ ) and data ( $D_0$ - $D_7$ ) lines used to interface with program/data memory.

**P2<sub>0</sub>-P2<sub>7</sub>.** *I/O Port Lines* (input/outputs, TTL compatible). 8 lines bit programmable. In addition they can be configured to provide open-drain output.

**P3<sub>0</sub>-P3<sub>7</sub>.** I/O Port Lines (TTL compatible) 4 lines input (P3<sub>0</sub>-P3<sub>3</sub>), 4 lines output P3<sub>4</sub>-P3<sub>7</sub>). They can also be configured as control lines.

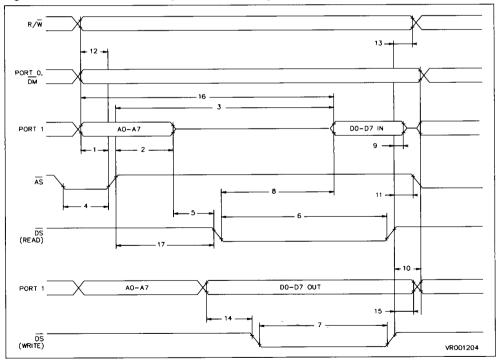

**AS.** Address Strobe (output, active Low). Address Strobe is pulsed once at the beginning of each machine cycle. Addresses output via Port 1 for all

external program or data memory transfers are valid at the trailing edge of  $\overline{AS}$ . Under program control,  $\overline{AS}$  can be placed in the high-impedance state along with ports 0 and 1, Data Strobe and Read/Write.

**DS**. *Data Strobe* (output, active Low). Data Strobe is activated once for each external memory transfer.

**RESET.** Reset (input, active Low). RESET initializes the Z86xx. When RESET is deactivated, program execution begins from internal program location 000CH.

**R/W.** Read/Write (output).  $R/\overline{W}$  is Low when the Z86xx is writing to external program or data memory.

XTAL1, XTAL2. Crystal 1, Crystal 2 (time-base input and output). These pins connect a parallel-resonant crystal (8 or 12MHz maximum) or an external single-phase clock (8 or 12MHz maximum) to the on-chip clock oscillator and buffer.

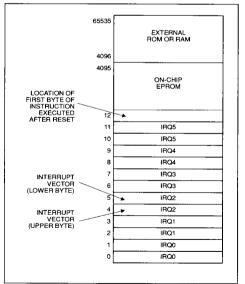

#### ADDRESS SPACES

**Program Memory.** The 16-bit program counter addresses 64K bytes of program memory space. Program memory can be located in two areas: one internal and the other external (figure 4). The first 4096 bytes consist of on-chip EPROM. At addresses 4096 and greater, the Z86E11 executes external program memory fetches.

The first 12 bytes of program memory are reserved for the interrupt vectors. These locations contain six 16-bit vectors that correspond to the six available interrupts.

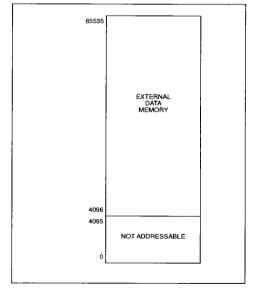

**Data Memory.** The Z86E11 can address 60K bytes of external data memory beginning at locations 4096 (figure 5). External data memory may be included with or separated from the external program memory space.

DM, an optional I/O function that can be programmed to appear on pin P34, is used to distinguish between data and program memory space.

**Register File.** The 144-byte register file includes four I/O port registers (R0-R3), 124 general-purpose registers (R4-R127) and 16 control and status registers (R240-R255). These registers are assigned the address locations shown in figure 6.

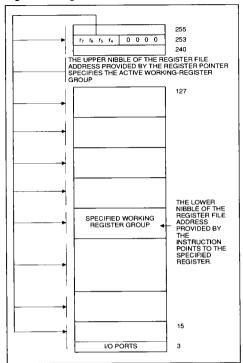

Z86E11 instructions can access registers directly or indirectly with an 8-bit address field. The Z86E11 also allows short 4-bit register addressing using the Register Pointer (one of the control registers). In this case, the register file is divided into nine working-register groups, each occupying 16 contiguous locations (figure 7). The Register Pointer addresses the starting location of the active working-register group.

Stacks. Either the internal register file or the external data memory can be used for the stack. A 16-bit Stack Pointer (R254 and R255) is used for the external stack, which can reside anywhere in data memory between locations 4096 and 65535. An 8-bit Stack Pointer (R255) is used for the internal stack that resides within the 124 general-purpose registers (R4-R127).

Figure 4: Program Memory Map.

Figure 5 : Data Memory Map.

# **ADDRESS SPACES** (Continued)

Figure 6: Register File.

**SERIAL INPUT/OUTPUT**

Port 3 lines P30 and P37 can be programmed as serial I/O lines for full-duplex serial asynchronous receiver/transmitter operation. The bit rate is controlled by Counter/Timer 0, with a maximum rate of 62.5K bits/second, for the 8MHz version.

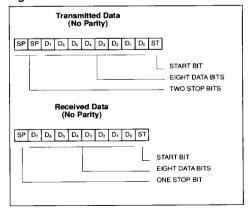

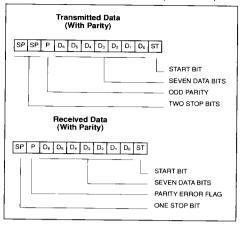

The Z8 automatically adds a start bit and two stop bits to transmitted data (figure 8). Odd parity is also available as an option. Eight data bits are always transmitted, regardless of parity selection. If parity is enabled, the eighth bit is the odd parity bit. An interrupt request (IRQ4) is generated on all transmitted characters.

Received data must have a start bit, eight data bits and at least one stop bit. If parity is on, bit 7 of the received data is replaced by a parity error flag. Received characters generate the IRQ3 interrupt request.

Figure 7: Register Pointer.

Figure 8 : Serial Data Formats.

# SERIAL INPUT/OUTPUT (Continued)

Figure 9 : Serial Data Formats (Continued)

# COUNTER/TIMERS

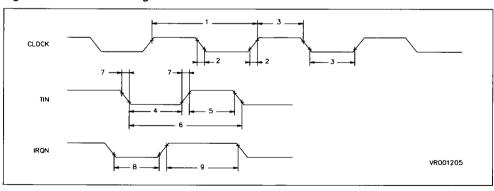

The Z8 contains two 8-bit programmable counter/timers ( $T_0$  and  $T_1$ ), each driven by its own 6-bit programmable prescaler. The  $T_1$  prescaler can be driven by internal or external clock sources; however, the  $T_0$  prescaler is driven by the internal clock only.

The 6-bit prescaler can divide the input frequency of the clock source by any number from 1 to 64. Each prescaler drives its counter, which decrements the value (1 to 256) that has been loaded into the counter. When the counter reaches the end of count, a timer interrupt request,  $IRQ_4$  ( $T_0$ ) or  $IRQ_5$  ( $T_1$ ), is generated.

The counters can be started, stopped, restarted to continue, or restarted from the initial value. The counters can also be programmed to stop upon reaching zero (single-pass mode) or to automatically reload the initial value and continue counting (modulo-n continuous mode). The counters, but not the prescalers, can be read any time without disturbing their value or count mode.

The clock source for  $T_1$  is user-definable and can be the internal microprocessor clock, 4MHz maximum for the 8MHz device and 6MHz maximum for the 12MHz device, divided by four, or an external signal input via Port 3. The Timer Mode register configures the external timer input as an external clock (1.5MHz maximum), a trigger input that can be retriggerable or non-retriggerable, or as a gate input for the internal clock. The counter/timers can be programmably cascated by connecting the  $T_0$

output to the input of  $T_1$ . Port 3 line  $P3_6$  also serves as a timer output ( $T_{OUT}$ ) through which  $T_0$ ,  $T_1$  or the internal clock can be output.

#### I/O PORTS

The Z8 has 32 lines dedicated to input and output. These lines are grouped into four ports of eight lines each and are configurable as input, output or address/data. Under software control, the ports can be programmed to provide address outputs, timing, status signals, serial I/O, and parallel I/O with or without handshake. All ports have active pull-ups and pull-downs compatible with TTL loads.

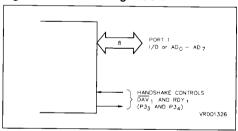

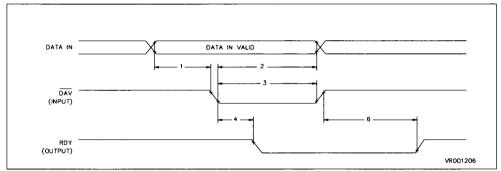

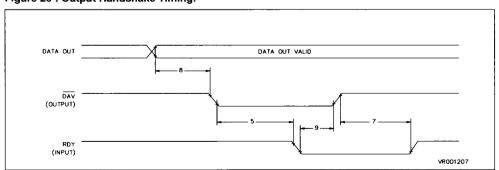

Port 1 can be programmed as a byte I/O port or as an address/data port for interfacing external memory. When used as an I/O port, Port 1 may be placed under handshake control. In this configuration, Port 3 lines  $P3_3$  and  $P3_4$  are used as the handshake controls  $RDY_1$  and  $DAV_1$  (ready and data available).

Memory locations greater than 4096 are referenced through Port 1. To interface external memory, Port 1 must be programmed for the multiplexed Address/Data mode. If more than 256 external locations are required, Port 0 must output the additional lines.

Port 1 can be placed in the high-impedance state along with Port 0, AS, DS and R/W, allowing the Z8 to share common resources in multiprocessor and DMA applications. Data transfers can be controlled by assigning P3<sub>3</sub> as a Bus Acknowledge input and P3<sub>4</sub> as a Bus Request output.

Figure 10 : Port 1 Configuration.

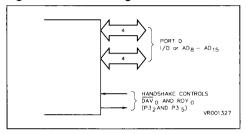

Port 0 can be programmed as a nibble I/O port, or as an address port for interfacing external memory. When used as an I/O port, Port 0 may be placed under handshake control. In this configuration, Port 3 lines  $P3_2$  and  $P3_5$  are used as the handshake controls  $DAV_0$  and  $RDY_0$ . Handshake signal assignment is dictated by the I/O direction of the upper nibble  $P0_4$ - $P0_7$ .

# I/O PORTS (Continued)

For external memory references, Port 0 can provide address bits  $A_8$ - $A_{11}$  (lower nibble) or  $A_{12}$ - $A_{15}$  (lower and upper nibble) depending on the required address space. If the address range requires 12 bits or less, the upper nibble of Port 0 can be programmed independently as I/O while the lower nibble is used for addressing. When Port 0 nibbles are defined as address bits, they can be set to the high-impedance state along with Port 1 and the control signals  $\overline{AS}$ ,  $\overline{DS}$  and  $\overline{R/W}$ .

Figure 11: Port O Configuration.

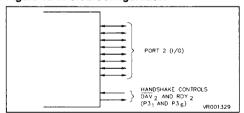

**Port 2** bits can be programmed independently as input or output. This port is always available for I/O operations. In addition, Port 2 can be configured to provide open-drain outputs.

Like Ports 0 and 1, Port 2 may also be placed under handshake control. In this configuration, Port 3 lines P3 $_1$  and P3 $_6$  are used as the handshake controls lines DAV $_2$  and RDY $_2$ . The handshake signal assignment for Port 3 lines P3 $_1$  and P3 $_6$  is dictated by the direction (input or output) assigned to bit 7 of Port 2.

Figure 12: Port 2 Configuration.

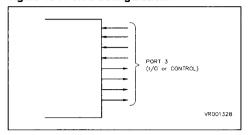

**Port 3** lines can be configured as I/O or control lines. In either case, the direction of the eight lines is fixed as four input (P3<sub>0</sub>-P3<sub>3</sub>) and four output (P3<sub>4</sub>-P3<sub>7</sub>). For serial I/O, lines P3<sub>0</sub> and P3<sub>7</sub> are programmed as serial in and serial out respectively.

Port 3 can also provide the following control functions: handshake for Ports 0, 1 and 2 (DAV and

RDY); four external interrupt request signals (IRQ<sub>0</sub>-IRQ<sub>3</sub>); timer input and output signals (T<sub>IN</sub> and T<sub>OUT</sub>) and Data Memory Select (DM).

Figure 13: Port 3 Configuration.

#### INTERRUPTS

The Z8 allows six different interrupts from eight sources: the four Port 3 lines P3<sub>0</sub>-P3<sub>3</sub>, Serial In, Serial Out, and the two counter/timers. These interrupts are both maskable and prioritized. The Interrupt Mask register globally or individually enables or disables the six interrupt requests. When more than one interrupt is pending, priorities are resolved by a programmable priority encoder that is controlled by the Interrupt Priority register.

All Z8 interrupts are vectored. When an interrupt request is granted, an interrupt machine cycle is entered. This disables all subsequent interrupts, saves the Program Counter and status flags, and branches to the program memory vector location reserved for that interrupt. This memory location and the next byte contain the 16-bit address of the interrupt service routine for that particular interrupt request.

Polled interrupt systems are also supported. To accommodate a polled structure, any or all of the interrupt inputs can be masked and the Interrupt Request register polled to determine which of the interrupt requests needs service.

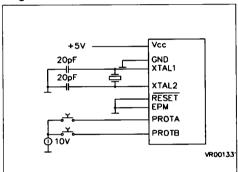

#### CLOCK

The on-chip oscillator has a high-gain, parallel-resonant amplifier for connection to a crystal or to any suitable external clock source (XTAL1 = Input, XTAL2 = Output).

The crystal source is connected across XTAL1 and XTAL2, using the recommended capacitors ( $C_1 \le 15pF$ ) from each pin to ground. The specifications for the crystal are as follows:

- AT cut, series resonant

- Fundamental types, 8MHz and 12MHz

- Series resistance,  $R_S$  ≤ 100 $\Omega$ .

SGS-THOMSON MICROFFLECTRONICS

# **EPROM MODE**

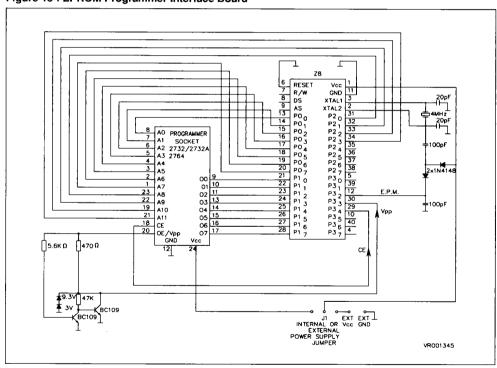

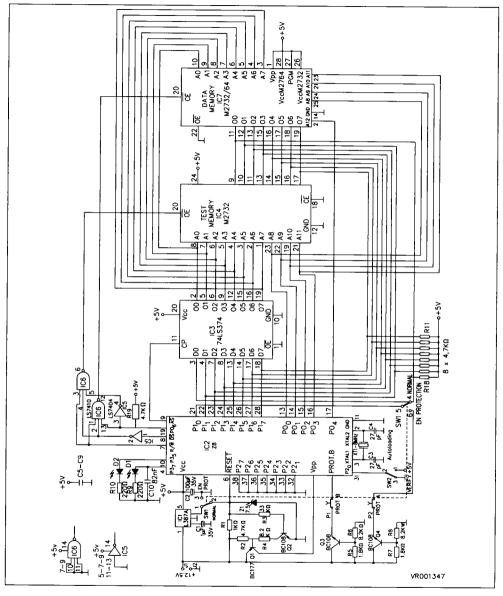

**Eprom-Like Programming.** In this mode, the microcomputer memory is programmed, using a standard EPROM programmer, with the same procedure as for our M2732 (32K bits EPROM). This made possible by the following Z86E11 configuration, where P1<sub>0</sub>-P1<sub>7</sub> are used as 8-bit I/O data (O<sub>0</sub>-O<sub>7</sub>), P0<sub>0</sub>-P0<sub>7</sub> and P2<sub>0</sub>-P2<sub>3</sub> are used as 12-bit Addresses (A<sub>0</sub>-A<sub>11</sub>); the microcomputer must be in Reset state, forcing the related pin to GND, and the Clock must be active for the complete operation.

Three other pins are available for that purpose: the EPM pin on port P3<sub>2</sub>, which allows the microcomputer to recognize the Eprom-Like condition when a high voltage (≥ 7V) is applied; the Vpp pin on port P3<sub>3</sub>, which is used to furnish programming voltage fixed at 12.5V±300mV; and the ČE pin on port P3<sub>4</sub>, which is used to perform program enable/verify.

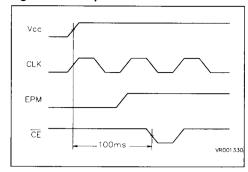

For a correct microcomputer set-up, the V<sub>CC</sub> must be applied at least 100ms before the programming procedure starts, as shown in Figure 14.

Figure 14: Set-up Waveforms

A simple interface board, described in Figure 15, allows programming to be carried out through use of a standard EPROM-programmer.

Figure 15: EPROM Programmer Interface Board

8/

This board can be used with a general purpose EPROM programmer without doing particular controls (power consumption, etc.) before starting the programming procedure.

This means that the board cannot be used with DATA I/O programmers. In fact it implements the above-mentioned controls, giving an error message and stopping the programming procedure when, for example, the power consumption of the Z86E11 is tested. This occurs because the MCU's power consumption is greater then the consumption of an M2732, due to the on-chip oscillator running on the microcomputer.

To solve this problem, an agreement with DATA I/O has been made with the purpose of designing a special cartridge for the DATA I/O 29B model, which use on-board the UNIPAK 2B firmware.

This cartridge, which is able to program the Z86E11 plus its relevant protection, is directly sold by DATA I/O with the order code 351B-Z8.

Self-Programming. This mode permits programming one byte of the on-chip EPROM during normal microcomputer program execution. The instruction to be used is the Load Constant LDC @RR0.R2 (operating code D2H).

This instruction allows the standard Z8 to load the content of the working register R2 into an external RAM memory allocated in the program memory space, (the address of the memory location is pointed by the pair of working registers R0 and R1). The Z86E11 uses this instruction also to program the 4K bytes on-chip EPROM.

Addressing one of the on-chip EPROM bytes, using this instruction, the programming operation takes place when an high voltage level on the VPP pin  $(12.5V \pm 300mV)$  is applied.

In this case, both the address and the data memory are stored internally for the necessary programming time, where the time is defined by the execution of 1024 NOP operations (1 NOP operation = 12 external clock pulses). The programming time is contained between 1ms (12MHz external clock) and 12ms (1MHz external clock).

As just mentioned, during this time, the CPU is automatically internally forced to execute NOP instructions (operating code FFH), while a RET instruction (operating code AFH) is automatically executed at the end of programming.

For a correct program restart is necessary to save the address of the Load Constant (LDC) next instruction in the Stack. This can be done by loading into the Stack the return address calling a Subroutine as below, where, to permit a correct return to the main program, it is necessary to disable the interrupt before LDC execution.

WRITE LDC @RR0,R2

RET (automatically executed)

Autoloading/Verify Facility. The most flexible way for on-chip EPROM programming is, as we know, the use of a standard EPROM programmer, selecting the Eprom-like facility, and using an appropriate interface board (Figure 15).

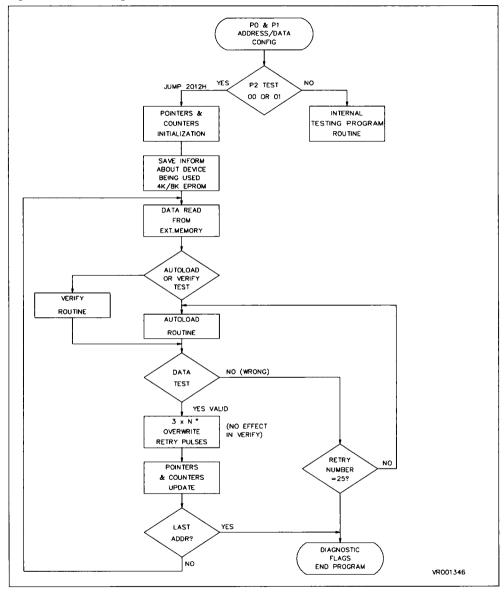

If, however, the planned operation is only a particular memory loading into the on-chip EPROM, it is possible to perform this operation in a much simpler way, using a board which allows the Z86E11 to read and load the renamed particular memory, using the autoloading procedure. Figure 16 shows the autoloading program flow-chart.

The software required for this operation is stored in an external Test-Memory, present in the auto-loading/verify board (IC4, Figure 17) and is listed in Table 1.

When the microcomputer is forced in Test mode by applying a high voltage level (≥ 7V) on the RESET pin, ports P0 and P1 are configured as address/data to access the external memory, only if either the values 00 or 01 are forced on port P2.

At this point, a test on port P2 is executed to decide if the on-chip EPROM Autolading or verify facility has to be executed.

Consequently, registers required for the operation are initialized, data to be compared or stored is read, and the routine chosen is executed.

The autoloading routine is an intelligent program which executes a number of overwriting cycles equal to three times the number of programming cycles required to perform a correct byte programming (up to a maximum of 25). Thus, the on-chip 4K EPROM programming time is optimized and equal to 25 seconds with an 8MHz external clock.

Figure 16: Autoloading Flow Chart

**Table 1. Test Memory Exadecimal Code**

| Addresses                                                                                                                                                                    |                                                                      |                                     |                                                                      |                                                                |                                                                      |                                                                      |                               |                                                 | Value                                              |                                                                |                                  |                                                                |                                                          |                                                          |                                                    |                               |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|-------------------------------------|----------------------------------------------------------------------|----------------------------------------------------------------|----------------------------------------------------------------------|----------------------------------------------------------------------|-------------------------------|-------------------------------------------------|----------------------------------------------------|----------------------------------------------------------------|----------------------------------|----------------------------------------------------------------|----------------------------------------------------------|----------------------------------------------------------|----------------------------------------------------|-------------------------------|

| 0000 to 000F<br>0010 to 001F<br>0020 to 002F<br>0030 to 003F<br>0040 to 004F<br>0050 to 005F<br>0060 to 006F<br>0070 to 007F<br>0080 to 008F<br>0090 to 009F<br>00A0 to 00AF | FF<br>FF<br>E9<br>FF<br>AF<br>CC<br>AB<br>E4<br>FF<br>FF<br>AF<br>8B | FF FF 40 FF D2 19 6B 8B FF FF A6 C1 | FF<br>FC<br>E6<br>FF<br>A6<br>C9<br>06<br>2E<br>FF<br>FF<br>3A<br>FF | FF<br>OE<br>FF<br>FF<br>FF<br>CA<br>3C<br>FF<br>FF<br>20<br>FF | FF<br>E7<br>3C<br>FF<br>FF<br>C2<br>F3<br>80<br>FF<br>FF<br>6B<br>FF | FF<br>EF<br>D6<br>FF<br>FF<br>A4<br>3C<br>8B<br>FF<br>FF<br>06<br>FF | FF 00 20 FF B0 20 FE FF 69 FF | FF FA A0 FF | FF<br>FB<br>8B<br>FF<br>D4<br>0C<br>FF<br>FF<br>CB | FF<br>4C<br>26<br>FF<br>E8<br>D4<br>FF<br>FF<br>FF<br>A6<br>FF | FF CO FF FF FF 66 E8 FF FF 8B FF | FF<br>8C<br>FF<br>FF<br>FF<br>FF<br>FF<br>FF<br>FF<br>FF<br>FF | FF<br>20<br>FF<br>FF<br>03<br>FC<br>FF<br>FF<br>69<br>FF | FF<br>98<br>FF<br>FF<br>C2<br>A0<br>FF<br>FF<br>FF<br>FC | FF<br>E2<br>FF<br>98<br>B6<br>E6<br>FF<br>FF<br>DB | FF 46 FF E2 A2 A0 FF FF A0 FF |

| 00C0 to 00CF<br>00D0 to 00DF<br>00E0 to 00EF<br>00F0 to 00FF                                                                                                                 | FF<br>FF<br>FF                                                       | FF<br>FF<br>FF                      | FF<br>FF<br>FF                                                       | FF<br>FF<br>FF<br>FF                                           | FF<br>FF<br>FF                                                       | FF<br>FF<br>FF                                                       | FF<br>FF<br>FF                | FF<br>FF<br>FF                                  | FF<br>FF<br>FF<br>FF                               | FF<br>FF<br>FF                                                 | FF<br>FF<br>FF                   | FF<br>FF<br>FF                                                 | FF<br>FF<br>FF                                           | FF<br>FF<br>FF                                           | FF<br>FF<br>FF                                     | FF<br>FF<br>FF                |

Note: All the other locations of the device were the test-memory is mapped (e.g. 2732 EPROM), between 100H and FFFH, are blank and contain the exadecimal value FF.

The verify routine is simply a byte-byte comparison between the external memory and the on-chip EPROM.

A possible failure, whether in Autoloading or Verify, produces a high logical level forced on P3s. Similarly, when the operation is finished, the positive conclusion is underlined, bringing P37 high.

An autoloading/Verify board diagram is shown in Figure 17, where the VPP line control is necessary to not allow high voltage into the device when it has not yet been supplied. Through this board is also possible to activate memory readout protection facility as explained below.

Memory Readout Protection. The protections, once activated, block reading memory content. Such reading can be carried out in two ways:

- Entering Eprom-Like Mode, using the Verify facility.

- Entering Test Mode you can execute an external memory program which allows the on-chip EPROM reading through LDC instruction execution.

Programming the first protection bit blocks reading in Eprom-Like Mode (PROTA on port P1<sub>0</sub>). Another protection bit (PROTB on port P0<sub>7</sub>) can be activated when the Z86E11 is in external memory configuration.

This protection prevents software manipulation of the external memory by someone who decides to read the on-chip EPROM content to have a complete understanding of the user application board.

When the Z86E11 works in the external memory facility, the ports P0 and P1 are configurated as an address/data bus, so that the external memory instructions can be executed during normal microcomputer operation. These instructions can be also an appropriate routine capable of pulling out all the on-chip memory content, using the LDC instruction.

When the protection PROTB is activated, any reading attempt of the internal memory content, using the LDC instruction, is becomes useless because the data out will be always "FFH".

Consequently this protection activation inhibits the LDC instruction execution from external to internal memory.

Figure 17: Autoloading/Verify and Readout Protection Activation Board

\_\_\_\_ **\**\\

The protections are activated by programming 2 non-volatile transistors simply forcing 10V for a time more than 100ms on the desired pin, on condition that the microcomputer is in Reset state, the Clock signal is present and the EPM pin is not set

If a complete protection is desired, both protections must be programmed.

A simple diagram for readout protection activation is shown in Figure 18.

To disable protections, a device exposure to short-wave ultraviolet light is required. In this way, also the on-chip EPROM content is erased. The EPROM array needs to be completely erased before its reprogramming and protection enabling.

Figure 18 : Readout Protection Activation Diagram

#### INSTRUCTION SET NOTATION

Addressing Modes. The following notation is used to describe the addressing modes and instruction operations as shown in the instruction summary.

| IRR | Indirect register pair or indirect working-<br>register pair address |

|-----|----------------------------------------------------------------------|

|     |                                                                      |

| Irr | Indirect working-register pair only                                  |

| Х   | Indexed address                                                      |

| DA  | Direct address                                                       |

| RA  | Relative address                                                     |

| IM  | Immediate                                                            |

| R   | Register or working-register address                                 |

| r   | Working - register adress only                                       |

address

Symbols The following symbols are used in

Indirect working-register address only

Register pair or working register pair

describing the instruction set.

dst Destination location or contents

src Source location or contents

cc Condition code (see list)

Indirect address prefix

SP Stack pointer (control registers 254-255)

PC Program counter

FLAGS Flag register (control register 252)

RP Register pointer (control register 253)

IMR Interrupt mask register

IR Interrupt mask register (control register 251).

Assignment of a value is indicated by the symbol "

—". For example,

dst ← dst + src

Ir

RR

indicates that the source data is added to the destination data and the result is stored in the destination location. The notation "addr(n)" is used to refer to bit "n" of a given location. For example,

dst (7)

refers to bit 7 of the destination operand.

Undefined

**Flags**. Control Register R252 contains the following six flags:

| С              | Carry flag       | h                  |       |          |      |       |             | ь0 |

|----------------|------------------|--------------------|-------|----------|------|-------|-------------|----|

| Z              | Zero flag        | b <sub>7</sub> C Z | S     | V        | ח    | Н     | F2          |    |

| S              | Sign flag        |                    |       | <u> </u> | _    | ı     | <u>. – </u> |    |

| V              | Overflow flag    |                    |       |          |      |       |             |    |

| D              | Decimal-adjust   | flag               | F1    | us       | er f | lag   |             |    |

| Н              | Half-carry flag  |                    | F2    | us       | er f | lag   |             |    |

| Affected flags | are indicated b  | <b>y</b> :         |       |          |      |       |             |    |

| 0              | Cleared to zero  |                    |       |          |      |       |             |    |

| 1              | Set to one       |                    |       |          |      |       |             |    |

| *              | Set or cleared a | accordin           | ng to | op       | oera | ation | 1           |    |

| -              | Unaffected       |                    |       |          |      |       |             |    |

x

# **CONDITION CODES**

| Value | Mnemonic | Meaning                        | Flags Set             |

|-------|----------|--------------------------------|-----------------------|

| 1000  |          | Always True                    |                       |

| 0111  | С        | Carry                          | C = 1                 |

| 1111  | NC       | No Carry                       | C = 0                 |

| 0110  | Z        | Zero                           | Z = 1                 |

| 1110  | NZ       | Not Zero                       | Z = 0                 |

| 1101  | PL       | Plus                           | S = 0                 |

| 0101  | MI       | Minus                          | S = 1                 |

| 0100  | OV       | Overflow                       | V = 1                 |

| 1100  | NOV      | No Overflow                    | V = 0                 |

| 0110  | EQ       | Equal                          | Z = 1                 |

| 1110  | NE       | Not Equal                      | Z = 0                 |

| 1001  | GE       | Greater than or Equal          | (S XOR V) = 0         |

| 0001  | LT       | Less than                      | (S XOR V) = 1         |

| 1010  | GT       | Greater than                   | [Z OR (S XOR V)] = 0  |

| 0010  | LE       | Less than or Equal             | [Z OR (S XOR V)] = 1  |

| 1111  | UGE      | Unsigned Greater than or Equal | C = 0                 |

| 0111  | ULT      | Unsigned less than             | C = 1                 |

| 1011  | UGT      | Unsigned greater than          | (C = 0 AND Z = 0) = 1 |

| 0011  | ULE      | Unsigned less than or equal    | (C OR Z) = 1          |

| 0000  |          | Never true                     |                       |

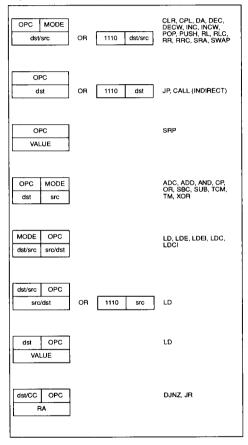

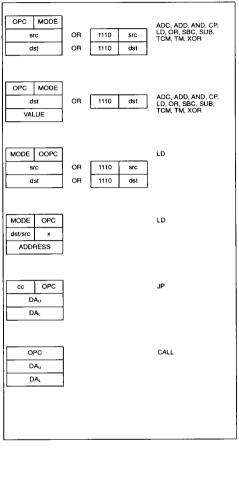

# INSTRUCTION FORMATS

# Figure 19: One-Byte Instruction Format.

# Figure 20: Two-bytes instruction Format.

Figure 21: Three-Bytes Instruction Format.

| Instruction                                                                                         | Addr Mo         | ode | Opcode<br>Byte            | F | lag | js A | ffe | cte | d |

|-----------------------------------------------------------------------------------------------------|-----------------|-----|---------------------------|---|-----|------|-----|-----|---|

| and Operation                                                                                       | dst s           | src | (Hex)                     | С | z   | s    | ٧   | D   | н |

| ADC dst, src<br>dst ← dst + src' + C                                                                | (Note           | 1)  | 1 🗆                       | • | •   |      | •   | 0   | • |

| ADD dst, src<br>dst ← dst + src                                                                     | (Note           | 1)  | 0 🗆                       |   |     |      | *   | 0   | • |

| AND dst, src<br>dst ← dst AND src                                                                   | (Note           | 1)  | 5 🗌                       | - | •   | •    | 0   | -   | - |

| CALL dst<br>SP ← SP - 2<br>@SP ← PC ; PC ← dst                                                      | DA<br>IRR       |     | D6<br>D4                  | • | -   | -    | -   | -   | - |

| CCF<br>C ← NOT C                                                                                    |                 |     | EF                        | * | -   | -    | -   | -   | - |

| CLR dst<br>dst ← 0                                                                                  | R<br>IR         |     | B0<br>B1                  | - | -   | -    | ~   | -   | - |

| COM dst<br>dst ← NOT dst                                                                            | R<br>IR         |     | 60<br>61                  | - | *   | *    | 0   | -   | - |

| CP dst, src<br>dst - src                                                                            | (Note 1         | 1)  | А                         | * | *   |      |     | -   | - |

| <b>DA</b> dst<br>dst ← DA dst                                                                       | R<br>IR         |     | 40<br>41                  |   | *   | •    | х   | -   | - |

| DEC dst<br>dst ← dst - 1                                                                            | R<br>IR         |     | 00<br>01                  | - | *   | *    | *   | -   | - |

| DECW dst<br>dst ← dst - 1                                                                           | RR<br>IR        |     | 80<br>81                  | - | *   | •    |     | -   | - |

| <b>DI</b><br>IMR (7) ← 0                                                                            |                 |     | 8F                        | - | -   | -    | -   | -   | - |

| <b>DJNZ</b> r, dst $r \leftarrow r - 1$ if $r \neq 0$ PC $\leftarrow$ PC + dst Range : + 127, - 128 | RA              |     | rA<br>r = 0 - F           | - | -   | -    | -   | -   |   |

| <b>EI</b><br>IMR (7) ← 1                                                                            |                 |     | 9F                        | - | -   | -    | -   | -   | - |

| INC dst<br>dst ← dst + 1                                                                            | r<br>R<br>IR    | ,   | rE<br>= 0 - F<br>20<br>21 | - | *   |      | *   | -   | - |

| INCW dst<br>dst ← dst + 1                                                                           | RR<br>IR        |     | A0<br>A1                  |   | •   |      |     | -   | - |

| IRET<br>FLAGS ← @SP; SP ←<br>PC ← @SP; SP ← SP ←<br>IMR (7) ← 1                                     | SP + 1<br>- 2 ; |     | BF                        |   | *   | *    | •   | ٠   |   |

| JP cc, dst<br>if cc is true<br>PC ← dst                                                             | DA<br>IRR       | (   | cD<br>= 0 - F<br>30       | - | -   | -    | -   | -   | - |

| JR cc, dst<br>if cc is true,<br>PC ← PC + dst<br>Range : + 127, - 128                               | RA              | c   | cB<br>= 0 - F             | - | -   | -    | -   | -   | - |

| Instruction                                                  | Addr        | Mode                | Opcode<br>Byte                               | F | laç | js A | Affe | cte | d |

|--------------------------------------------------------------|-------------|---------------------|----------------------------------------------|---|-----|------|------|-----|---|

| and Operation                                                | dst         | src                 | (Hex)                                        | С | z   | s    | ٧    | D   | н |

|                                                              | r<br>r<br>R | lm<br>R<br>r        | rC<br>r8<br>r9<br>r = 0 - F<br>C7            |   |     |      |      |     |   |

| LD dst, src<br>dst ← src                                     | XrlrRRRRR   | r Ir r R IR IM IM R | D7<br>E3<br>F3<br>E4<br>E5<br>E6<br>E7<br>F5 | - | -   | -    | -    | -   | • |

| LDC dst, src<br>dst ← src                                    | r<br>Irr    | lrr<br>r            | C2<br>D2                                     | - | -   | -    | -    | -   | - |

| LDCI dst,src<br>dst ← src<br>r ← r + 1 ; rr ← rr + 1         | lr<br>Irr   | lrr<br>Ir           | C3<br>D3                                     | - | -   | -    | -    | -   | - |

| LDE dst, src<br>dst ← src                                    | r<br>Irr    | Irr<br>r            | 82<br>92                                     | - | -   | -    | -    | -   | - |

| <b>LDEI</b> dst, src<br>dst ← src<br>r ← r + 1 ; rr ← rr + 1 | lr<br>Irr   | lrr<br>Ir           | 83<br>93                                     | - | -   | -    | -    | -   | - |

| NOP                                                          |             |                     | FF                                           | - | -   |      | -    | -   | - |

| OR dst, src<br>dst ← dst OR src                              | (No         | te 1)               | 4                                            | - | *   | *    | 0    | -   | - |

| <b>POP</b> dst<br>dst ← @ SP<br>SP ← SP + 1                  | R<br>IR     |                     | 50<br>51                                     | - |     | -    | -    | -   |   |

| <b>PUSH</b> src<br>SP ← SP - 1 ; @ SP ← s                    | rc          | R<br>IR             | 70<br>71                                     | - | -   | -    | -    | -   |   |

| <b>RCF</b><br>C ← 0                                          |             |                     | CF                                           | 0 | -   | -    | -    | -   | - |

| <b>RET</b><br>PC ← @ SP ; SP ← SP +                          | - 2         |                     | AF                                           | - | -   |      | -    | -   | - |

| RL dst                                                       | R<br>IR     |                     | 90<br>91                                     |   | •   | *    | *    | -   | - |

| RLC dst 7 0                                                  | R<br>IR     |                     | 10<br>11                                     | * | •   | •    | *    | -   | - |

| RR dst FC F7 0                                               | R<br>IR     |                     | E0<br>E1                                     | • | •   | •    | •    | -   | - |

| RRC dst 7 0                                                  | R           |                     | C0<br>C1                                     |   |     |      |      | -   | - |

| SBC dst, src<br>dst ← dst - src - C                          | (Not        | e 1)                | 3 🗌                                          | • | *   | •    | •    | 1   | ٠ |

Note: 1. These instructions have an identical set of addressing modes, which are encoded for brevity. The first opcode nibble is found in the instruction set table above. The second nibble is expressed symbolically by a  $\ensuremath{\square}$  in this table, and its value is found in the following table to the left of the applicable addressing mode pair. For example, the opcode of an ADC instruction using the addressing modes r (destination) and Ir (source) is 13.

| Instruction                       | Addr    | Mode  | Opcode<br>Byte | F | laç | js A | Affe | cte | d |

|-----------------------------------|---------|-------|----------------|---|-----|------|------|-----|---|

| and Operation                     | dst src |       | (Hex)          | С | z   | s    | ٧    | D   | н |

| <b>SCF</b> C ← 1                  |         |       | DF             | 1 | -   | -    | -    | -   | - |

| SRA dst C 7 0                     | R<br>IR |       | D0<br>D1       | • | •   | •    | 0    | -   | - |

| SRP src<br>RP ← src               |         | lm    | 31             | - | -   | -    | -    | -   | - |

| SUB dst, src<br>dst ← dst - src   | (No     | te 1) | 2              | * | ٠   | ٠    | *    | 1   | • |

| SWAP dst 7 4 3 0                  | I R     |       | F0<br>F1       | х | •   | •    | x    | -   | - |

| TCM dst, src<br>(NOT dst) AND src | (No     | te 1) | 6              | - |     |      | 0    | -   | - |

| TM dst, src<br>dst AND src        | (No     | te 1) | 7              | - |     | •    | 0    | -   | - |

| XOR dst, src<br>dst ← dst XOR src | (No     | te 1) | В              | - | •   |      | 0    | -   |   |

|   | Addr | Mode | Lower         |  |

|---|------|------|---------------|--|

| - | dst  | src  | Opcode Nibble |  |

|   | r    | r    | 2             |  |

|   | r    | Ir   | 3             |  |

|   | R    | R    | 4             |  |

|   | R    | IR   | 5             |  |

|   | R    | IM   | 6             |  |

Note: 1.These instructions have an identical set of addressing modes, which are encoded for brevity. The first opcode nibble is found in the instruction set table above. The second nibble is expressed symbolically by a D in this table, and its value is found in the following table to the left of the applicable addressing mode pair. For example, the opcode of an ADC instruction using the addressing modes r (destination) and Ir (source) is 13.

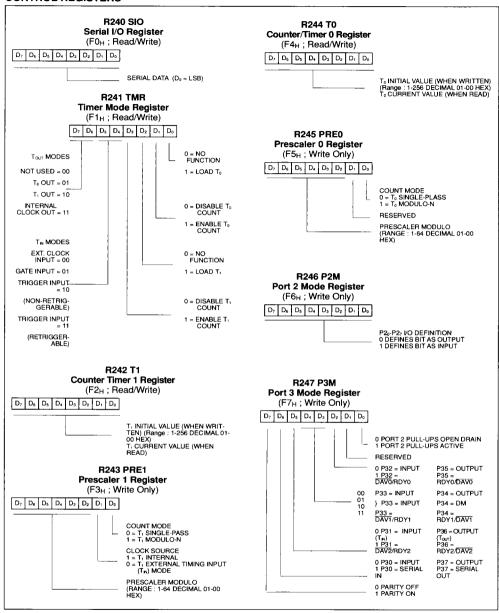

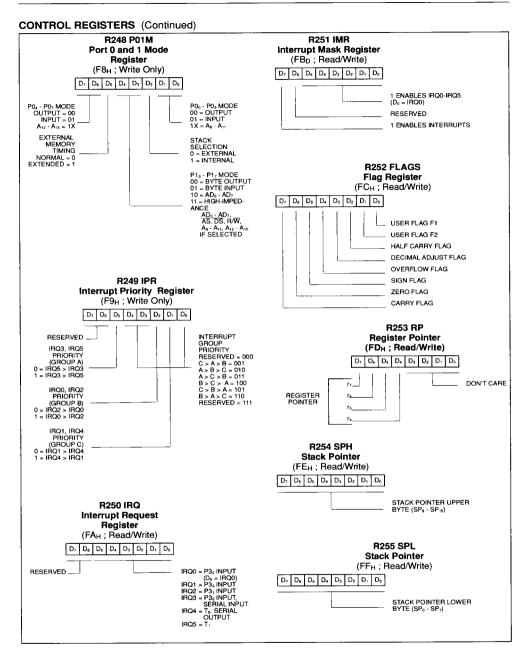

### **CONTROL REGISTERS**

18/

|     |                         |                        |                                         |                                            |                                                  |                                         | Lower                      | r Nibble                                 | (Hex)                                 |                                       |                |              |                           |              | -         |          |

|-----|-------------------------|------------------------|-----------------------------------------|--------------------------------------------|--------------------------------------------------|-----------------------------------------|----------------------------|------------------------------------------|---------------------------------------|---------------------------------------|----------------|--------------|---------------------------|--------------|-----------|----------|

|     | 0                       | 1_                     | 2                                       | 3_                                         | _ 4                                              | 5                                       | 6                          | 7                                        | 8                                     | 9                                     | Α              | В            | С                         | D            | E         |          |

| 0   | 6, 5<br><b>DEC</b>      | 6, 5<br><b>DEC</b>     | 6, 5<br>ADD                             | 6, 5<br>ADD                                | 10, 5<br>ADD                                     | 10, 5<br>ADD                            | 10, 5<br>ADD               | 10, 5<br>ADD                             | 6, 5                                  | 6, 5                                  | 12/10, 5       | 12/10, 0     | 6, 5                      | 12/10, 0     | 6, 5      | Т        |

| ·   | R <sub>1</sub>          | IR,                    | r <sub>1</sub> , r <sub>2</sub>         | r <sub>1</sub> , lr <sub>2</sub>           | R <sub>2</sub> , R <sub>1</sub>                  | IR <sub>2</sub> , R <sub>1</sub>        | R <sub>1</sub> , IM        | IR <sub>1</sub> , IM                     | LD<br>r <sub>1</sub> , R <sub>2</sub> | LD<br>r <sub>2</sub> , R <sub>1</sub> | DJNZ<br>rı, RA | JR<br>cc, RA | LD<br>r <sub>1</sub> , IM | JP<br>cc, DA | INC<br>r: |          |

|     | 6, 5                    | 6, 5                   | 6, 5                                    | 6, 5                                       | 10, 5                                            | 10, 5                                   | 10, 5                      | 10, 5                                    |                                       |                                       | "              |              | 1                         | 1 30,5%      | ï         | $\vdash$ |

| 1   | RLC                     | RLC                    | ADC                                     | ADC                                        | ADC                                              | ADC                                     | ADC                        | ADC                                      |                                       |                                       |                |              |                           |              |           |          |

|     | R <sub>1</sub>          | IR,                    | r <sub>1</sub> , r <sub>2</sub>         | r1, Ir2                                    | R <sub>2</sub> , R <sub>1</sub>                  | IR₂, R₁                                 | R <sub>1</sub> , IM        | IR <sub>1</sub> , IM                     |                                       |                                       | i              |              | İ                         |              |           | ľ        |

| 2   | 6, 5                    | 6, 5                   | 6, 5                                    | 6, 5                                       | 10,5                                             | 10, 5                                   | 10, 5                      | 10, 5                                    |                                       |                                       |                |              |                           |              |           | Г        |

| 2   | INC<br>R <sub>1</sub>   | INC<br>IR <sub>1</sub> | SUB<br>(1, [2                           | SUB<br>r <sub>1</sub> , lr <sub>2</sub>    | SUB<br>R <sub>2</sub> , R <sub>1</sub>           | SUB<br>IR <sub>2</sub> , R <sub>1</sub> | SUB<br>R <sub>1</sub> , IM | SUB<br>IR., IM                           |                                       |                                       |                |              |                           |              |           | İ        |

|     | 8, 0                    | 6, 1                   | 6, 5                                    | 6, 5                                       | 10, 5                                            | 10, 5                                   | 10, 5                      | 10, 5                                    |                                       |                                       |                |              |                           |              |           | <u> </u> |

| 3   | JP                      | SRP                    | SBC                                     | SBC                                        | SBC                                              | SBC                                     | SBC                        | SBC                                      |                                       |                                       |                |              |                           |              |           | İ        |

|     | IRR.                    | IM                     | r1, r2                                  | r <sub>1</sub> , Ir <sub>2</sub>           | R <sub>2</sub> , R <sub>1</sub>                  | IR <sub>2</sub> , R <sub>1</sub>        | R <sub>1</sub> , IM        | IR <sub>1</sub> , IM                     |                                       |                                       |                |              |                           |              |           |          |

|     | 8, 5                    | 8, 5                   | 6, 5                                    | 6, 5                                       | 10, 5                                            | 10, 5                                   | 10, 5 10, 5                |                                          |                                       |                                       |                |              |                           |              |           | $\vdash$ |

| 4   | DA                      | DA                     | OR                                      | OR                                         | OR                                               | OR                                      | OR                         | OR                                       | '                                     | -                                     |                |              | ļ                         |              |           |          |

|     | R <sub>1</sub>          | IR,                    | r <sub>1</sub> , r <sub>2</sub>         | r <sub>1</sub> , lr <sub>2</sub>           | R <sub>2</sub> , R <sub>1</sub>                  | IR <sub>2</sub> , R <sub>1</sub>        | R <sub>1</sub> , IM        | IR <sub>1</sub> , IM                     |                                       |                                       |                |              |                           | 1 [ ]        |           |          |

| 5   | 10, 5<br>POP            | 10, 5<br><b>POP</b>    | 6, 5                                    | 6, 5                                       | 10, 5                                            | 10, 5                                   | 10, 5                      | 10, 5                                    |                                       |                                       | !              | 1 1          |                           | 1   1        |           |          |

| 3   | R,                      | IR,                    | AND<br>r1, r2                           | AND<br>r <sub>1</sub> , lr <sub>2</sub>    | AND<br>R <sub>2</sub> , R <sub>1</sub>           | AND<br>IR <sub>2</sub> , R <sub>1</sub> | AND<br>R <sub>1</sub> , IM | AND<br>IR <sub>1</sub> , IM              | 1 1                                   |                                       |                | - 1 1        |                           |              |           |          |

|     | 6, 5                    | 6, 5                   | 6, 5                                    | 6, 5                                       | 10, 5                                            | 10, 5                                   | 10, 5                      | 10, 5                                    | 11                                    |                                       |                |              |                           |              |           | L        |

| 6   | СОМ                     | СОМ                    | TCM                                     | TCM                                        | TCM                                              | TCM                                     | TCM                        | TCM                                      |                                       |                                       | !              | 1 1          |                           |              |           |          |

|     | R <sub>1</sub>          | IR,                    | r <sub>1</sub> , r <sub>2</sub>         | r <sub>1</sub> , Ir <sub>2</sub>           | R2, R1                                           | IR <sub>2</sub> , R <sub>1</sub>        | R <sub>1</sub> , IM        | IR <sub>1</sub> , IM                     |                                       |                                       |                |              |                           |              |           | 1        |

| _   | 10/12, 1                | 12/14, 1               | 6, 5                                    | 6, 5                                       | 10, 5                                            | 10, 5                                   | 10, 5                      | 10, 5                                    |                                       |                                       |                |              |                           |              |           | Н        |

| 7   | PUSH                    | PUSH                   | TM                                      | TM                                         | TM                                               | TM                                      | TM                         | TM                                       |                                       |                                       |                |              |                           |              |           |          |

|     | R <sub>2</sub>          | IR <sub>2</sub>        | r <sub>1</sub> , r <sub>2</sub>         | r <sub>1</sub> , Ir <sub>2</sub>           | R <sub>2</sub> , R <sub>1</sub>                  | IR₂, R₁                                 | R₁, IM                     | IR <sub>1</sub> , IM                     |                                       | i                                     |                |              |                           |              |           | L        |

| 8   | 10, 5<br><b>DECW</b>    | 10, 5<br><b>DECW</b>   | 12, 0<br><b>LDE</b>                     | 18, 0<br><b>LDE</b> I                      |                                                  |                                         |                            |                                          |                                       |                                       |                |              |                           | 1            |           | l        |

| ٠   | RR,                     | IR,                    | r <sub>1</sub> , lrr <sub>2</sub>       | Ir <sub>1</sub> , Irr <sub>2</sub>         |                                                  |                                         |                            |                                          |                                       |                                       |                | - 1 1        |                           |              | - 1       |          |

|     | 6, 5                    | 6, 5                   | 12, 0                                   | 18, 0                                      | <del>                                     </del> |                                         |                            |                                          |                                       | Ì                                     |                |              |                           |              |           | H        |

| 9   | RL                      | RL                     | LDE                                     | LDEI                                       |                                                  |                                         | 1                          | 1 [                                      |                                       |                                       |                |              |                           |              |           | ŀ        |

|     | R <sub>1</sub>          | IR,                    | r <sub>2</sub> , lrr <sub>1</sub>       | Ir2, Irr;                                  |                                                  |                                         | <u>_</u>                   |                                          |                                       |                                       |                |              |                           |              |           |          |

|     | 10, 5                   | 10, 5                  | 6, 5                                    | 6, 5                                       | 10, 5                                            | 10, 5                                   | 10, 5                      | 10, 5                                    | - 1                                   |                                       |                |              |                           |              |           | ·        |

| A   | INCW<br>RR <sub>1</sub> | INCW                   | CP<br>r1, r2                            | CP<br>r <sub>1</sub> , lr <sub>2</sub>     | CP<br>R <sub>2</sub> , R <sub>1</sub>            | CP<br>IR <sub>2</sub> , R <sub>1</sub>  | CP<br>R <sub>1</sub> , IM  | CP<br>IR., IM                            |                                       |                                       | 1 1            |              |                           |              |           | F        |

|     | 6, 5                    | 6, 5                   | 6, 5                                    | 6, 5                                       | 10, 5                                            | 10, 5                                   | 10, 5                      |                                          | 11                                    |                                       |                |              | l i                       |              |           | L        |

| В   | CLR                     | CLR                    | XOR                                     | XOR                                        | XOR                                              | XOR                                     | XOR                        | 10, 5<br>XOR                             |                                       |                                       | 1              |              |                           |              |           | 1        |

|     | R <sub>1</sub>          | IR,                    | r <sub>1</sub> , r <sub>2</sub>         | r <sub>1</sub> , Ir <sub>2</sub>           | R <sub>2</sub> , R <sub>1</sub>                  | IR <sub>2</sub> , R <sub>1</sub>        | R <sub>1</sub> , IM        | IR <sub>1</sub> , IM                     |                                       |                                       |                |              |                           |              |           | "        |

|     | 6, 5                    | 6, 5                   | 12, 0                                   | 18, 0                                      |                                                  |                                         |                            | 10, 5                                    | 1 1                                   |                                       |                | 1 1          |                           |              |           | Н        |

| С   | RRC                     | RRC                    | LDC                                     | LDCI                                       |                                                  |                                         |                            | LD                                       |                                       |                                       |                | -            | İ                         |              | 1         | F        |

|     | R,                      | IR,                    | r <sub>1</sub> , lrr <sub>2</sub>       | Ir <sub>1</sub> , Irr <sub>2</sub>         |                                                  |                                         |                            | r <sub>1</sub> , x, R <sub>2</sub>       |                                       |                                       |                | 1 1          |                           |              |           |          |

| D   | 6, 5<br>SRA             | 6,5                    | 12, 0                                   | 18, 0                                      | 20, 0                                            |                                         | 20, 0                      | 10, 5                                    |                                       |                                       |                |              |                           |              |           |          |

| _   | SHA<br>R <sub>1</sub>   | SRA<br>IR,             | LDC<br>r <sub>2</sub> , lm <sub>1</sub> | LDCI<br>lr <sub>2</sub> , lrr <sub>1</sub> | CALL*                                            |                                         | CALL<br>DA                 | LD<br>r <sub>2</sub> , x, R <sub>1</sub> | -                                     | - 1                                   |                |              |                           |              |           | 5        |

|     | 6, 5                    | 6, 5                   |                                         | 6, 5                                       | 10,5                                             | 10, 5                                   | 10. 5                      | 10. 5                                    |                                       |                                       |                |              |                           |              |           | _        |

| E   | RR                      | RR                     |                                         | LD                                         | LD                                               | LD                                      | LD                         | LD                                       |                                       |                                       |                |              |                           |              |           | ď        |

|     | R <sub>1</sub>          | IR,                    |                                         | r1, Ir2                                    | R <sub>2</sub> , R <sub>1</sub>                  | IR <sub>2</sub> , R <sub>1</sub>        | R <sub>1</sub> , IM        | IR <sub>1</sub> , IM                     |                                       |                                       |                |              |                           |              |           | `        |

| _   | 6, 7                    | 6, 7                   |                                         | 6, 5                                       |                                                  | 10, 5                                   |                            |                                          |                                       |                                       |                |              |                           |              |           |          |

| F   | SWAP                    | SWAP                   |                                         | LD                                         |                                                  | LD                                      |                            | l                                        |                                       |                                       |                |              |                           |              |           | N        |

|     | R <sub>1</sub>          | IR <sub>1</sub>        |                                         | Ir <sub>1</sub> , r <sub>2</sub>           |                                                  | R <sub>2</sub> , IR <sub>1</sub>        |                            |                                          | +                                     | <b>*</b>                              | +              | +            | +                         | +            | <b>+</b>  | L        |

|     |                         |                        |                                         |                                            |                                                  |                                         |                            |                                          |                                       |                                       |                |              |                           |              |           |          |

| n., | tes per                 | 2                      | _                                       |                                            |                                                  |                                         |                            |                                          |                                       |                                       | 2              |              |                           |              |           | ı        |

Note: \* 2-byte instruction fetch cycle appears as a 3-byte instruction.

10, 5

CP

R<sub>2</sub>, R<sub>1</sub>

FIRST OPERAND >

20/

R1 or r1 = Dst address

R2 or R2 = Src address

Note: The blank areas are not defined.

Sequence: Opcode, First Operand, Second Operand

SECOND OPERAND

MNEMONIC

# **ABSOLUTE MAXIMUM RATINGS\***

| Symbol           | Parameter                             | Value       | unit |

|------------------|---------------------------------------|-------------|------|

|                  | Voltage on any pin relative to ground | -0.3 to 7.0 | ٧    |

| TA               | Operating Ambient Temperature         | 0 to 70     | ,C   |

| T <sub>STG</sub> | Storage Temperature                   | -65 to 150  | ,C   |

Note: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of these specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

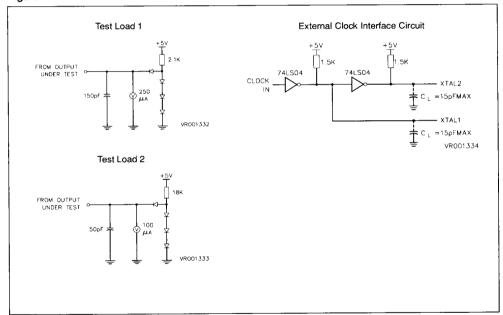

# **TEST CONDITIONS**

The characteristics below apply for the following standard conditions, unless otherwise noted. All voltages are referenced to GND. Positive current flows into the reference pin.

# Standard test conditions are as follows:

$- + 4.5 \le V_{CC} \le + 5.5V$

-GND = 0V

$-0^{\circ}C \leq T_A \leq +70^{\circ}C$

Figure 22: Test Circuits

# DC CHARACTERISTICS

| Symbol          | Parameter                      | Min. | Max. | unit | Condition                                      |

|-----------------|--------------------------------|------|------|------|------------------------------------------------|

| V <sub>CH</sub> | Clock input High Voltage       | 3.8  | Vcc  | V    | Driven by External Clock Generator             |

| V <sub>CL</sub> | Clock Input Low Voltage        | -0.3 | 0.8  | V    | Driven by External Clock Generator             |

| VIH             | nput High Voltage              | 2.0  | Vcc  | ٧    |                                                |

| VIL             | Input Low Voltage              | -0.3 | 0.8  | V    |                                                |

| V <sub>RH</sub> | Reset Input High Voltage       | 3.8  | Vcc  | ٧    |                                                |

| V <sub>RL</sub> | Reset Input Low Voltage        | -0.3 | 0.8  | V    |                                                |

| V <sub>OH</sub> | Output High Voltage            | 2.4  |      | ٧    | i <sub>OH</sub> = -250μA                       |

| VoL             | Output Low Voltage             |      | 0.4  | ٧    | I <sub>OL</sub> = +2.0mA                       |

| lıL             | Input Leakage                  | -10  | 10   | μА   | 0V ≤ V <sub>IN</sub> ≤ +5.25V                  |

| loL             | Output Leakage                 | -10  | 10   | μΑ   | 0V ≤ V <sub>IN</sub> ≤ +5.25V                  |

| I <sub>IR</sub> | Reset Input Current            |      | -50  | μА   | V <sub>CC</sub> = +5.25V, V <sub>RL</sub> = 0V |

| lcc             | V <sub>CC</sub> Supply Current |      | 180  | mA   |                                                |

| İpp             | V <sub>PP</sub> Supply Current | -    | 30   | mA   | CE = VIL                                       |

| V <sub>PP</sub> | EPROM Programming Voltage      | 12.2 | 12.8 | V    |                                                |

#### Notes:

- 1. Vcc must be applied simultaneously with or before VPP and removed simultaneously with or after VPP. The EPROM must not be

- inserted into or removed from a board with V<sub>PP</sub> activated or damage may occur to the device.

The maximum allowable voltage which may be applied to the V<sub>PP</sub> in during programming is 13V. Care must be taken when switching the V<sub>PP</sub> supply to prevent overshoot exceeding its maximum specification. 2.

# EXTERNAL I/O OR MEMORY, READ WRITE AND CLOCK CYCLE TIMING

| N. | Symbol                | Parameter                        |      | Z86E11/ | 8MHz                   | Z    | 86E11/ | 12MHz                  | Notes      |

|----|-----------------------|----------------------------------|------|---------|------------------------|------|--------|------------------------|------------|

|    | ,                     |                                  | Min. | Max.    | Equation               | Min. | Max.   | Equation               | Notes      |

| 1  | T <sub>DA(AS)</sub>   | Address Valid to AS ↑ Delay      | 50   |         | T <sub>PC</sub> - 75   | 35   |        | T <sub>PC</sub> - 50   | 1, 2, 3    |

| 2  | T <sub>DAS(A)</sub>   | AS ↑ to Address Float Delay      | 70   |         | T <sub>PC</sub> - 55   | 45   |        | T <sub>PC</sub> - 40   | 1, 2, 3    |

| 3  | T <sub>DAS(DR)</sub>  | AS ↑ to Read Data Required Valid |      | 360     | 4T <sub>PC</sub> - 140 |      | 220    | 4T <sub>PC</sub> - 110 | 1, 2, 3, 4 |

| 4  | Twas                  | AS Low Width                     | 80   |         | T <sub>PC</sub> - 45   | 55   |        | T <sub>PC</sub> - 30   | 1, 2, 3    |

| 5  | T <sub>DAZ(DS)</sub>  | Address Float to DS ↓            | 0    |         | 3T <sub>PC</sub> - 125 | 0    |        | 3T <sub>PC</sub> - 65  | 1          |

| 6  | Twdsr                 | DS (Read) Low Width              | 250  |         | 2T <sub>PC</sub> - 90  | 185  |        | 2T <sub>PC</sub> - 55  | 1, 2, 3, 4 |

| 7  | T <sub>WDSW</sub>     | DS (Write) Low Width             | 160  |         | 3T <sub>PC</sub> - 175 | 110  |        | 3T <sub>PC</sub> - 120 | 1, 2, 3, 4 |

| 8  | T <sub>DDSR(DR)</sub> | DS ↓ to Read Data Required Valid |      | 200     | T <sub>PC</sub> - 55   |      | 130    | T <sub>PC</sub> - 40   | 1, 2, 3, 4 |

| 9  | T <sub>HDR(DS)</sub>  | Read Data to DS ↓ Hold Time      | 0    |         |                        | 0    |        |                        | 1          |

| 10 | T <sub>DDS(A)</sub>   | DS ↑ to Address Active Delay     | 70   |         | T <sub>PC</sub> - 55   | 45   |        | T <sub>PC</sub> - 30   | 1, 2, 3    |

| 11 | T <sub>DDS(AS)</sub>  | DS ↑ to AS ↓ Delay               | 70   |         | T <sub>PC</sub> - 75   | 55   |        | T <sub>PC</sub> - 55   | 1, 2, 3    |

# EXTERNAL I/O OR MEMORY, READ WRITE AND CLOCK CYCLE TIMING (Continued)

| N. | Symbol                | Parameter                                    | Z86E11/8MHz |      |                        | Z    | Notes |                        |            |

|----|-----------------------|----------------------------------------------|-------------|------|------------------------|------|-------|------------------------|------------|

| "  |                       |                                              | Min.        | Max. | Equation               | Min. | Max.  | Equation               |            |

| 12 | T <sub>DR/W(AS)</sub> | R/W Valid to ĀŠ↑ Delay                       | 50          |      | T <sub>PC</sub> - 65   | 30   |       | T <sub>PC</sub> - 50   | 1, 2, 3    |

| 13 | T <sub>DDS(R/W)</sub> | DS ↑ to R/W Not Valid                        | 60          |      | T <sub>PC</sub> - 75   | 35   |       | T <sub>PC</sub> - 50   | 1, 2, 3    |

| 14 | T <sub>DDW(DSW)</sub> | Write Data Valid to DS<br>(Write) ↓ Delay    | 50          |      | T <sub>PC</sub> - 55   | 35   |       | T <sub>PC</sub> - 40   | 1, 2, 3    |

| 15 | T <sub>DDS(DW)</sub>  | DS ↑ to Write Data Not Valid<br>Delay        | 70          |      | 5T <sub>PC</sub> - 215 | 45   |       | 5T <sub>PC</sub> - 160 | 1, 2, 3    |

| 16 | T <sub>DA(DR)</sub>   | Address Valid to Read Data<br>Required Valid |             | 410  | T <sub>PC</sub> - 45   |      | 255   | T <sub>PC</sub> - 30   | 1, 2, 3, 4 |

| 17 | T <sub>DAS(DS)</sub>  | ĀS ↑ to DS ↓ Delay                           | 80          |      |                        | 55   |       |                        | 1, 2, 3    |

Notes: All values in ns.

Test Load 1. 1. 2. 3. 4.

Timing numbers given are for minimum TPC.

Also see clock cycle time dependent characteristics table. When using extended memory timing add 2 T<sub>P</sub>C.

Figure 23: External I/O or Memory Read/Write Timing.

SGS-THOMSON

# ADDITIONAL TIMING TABLE

| N. | Symbol                                | Parameter                         | Z86E1            | Z86E11/8MHz |                  | Z86E11/12MHz |      | Notes  |  |

|----|---------------------------------------|-----------------------------------|------------------|-------------|------------------|--------------|------|--------|--|

|    |                                       | Mir                               |                  | Max.        | Min.             | Max.         | Unit | 110.03 |  |

| 1  | T <sub>PC</sub>                       | Input Clock Period                | 125              | 1000        | 83               | 1000         | ns   | 1      |  |

| 2  | T <sub>RC</sub> , T <sub>FC</sub>     | Clock Input Rise And Fall Times   |                  | 25          |                  | 15           | ns   | 1      |  |

| 3  | Twc                                   | Input Clock Width                 | 37               |             | 26               |              | ns   | 1      |  |

| 4  | T <sub>WTINL</sub>                    | Timer Input Low Width             | 100              |             | 70               |              | ns   | 2      |  |

| 5  | T <sub>WTINH</sub>                    | Timer Input High Width            | 3T <sub>PC</sub> |             | 3T <sub>PC</sub> |              | ns   | 2      |  |

| 6  | T <sub>PTIN</sub>                     | Timer Input Period                | 8T <sub>PC</sub> |             | 8T <sub>PC</sub> |              | ns   | 2      |  |

| 7  | T <sub>RTIN</sub> , T <sub>FTIN</sub> | Timer Input Rise And Fall Times   |                  | 100         |                  | 100          | ns   | 2      |  |

| 8a | TwiL                                  | Interrupt Request Input Low Time  | 100              |             | 70               |              | ns   | 2, 3   |  |

| 8b | TwiL                                  | Interrupt Request Input Low Time  | 3T <sub>PC</sub> |             | 3T <sub>PC</sub> |              | ns   | 2, 4   |  |

| 9  | TwiH                                  | Interrupt Request Input High Time | 3T <sub>PC</sub> |             | 3T <sub>PC</sub> |              | ns   | 2, 3   |  |

# Notes :